# MOSTEK 1981 BYTEWYDE MEMORY DATA BOOK

# 1981 BYTEWYDE Products Data Book

Copyright© 1980 Mostek Corporation (All rights reserved) Trade Marks Registered® Mostek reserves the right to make changes in specifications at any time and without notice. The information furnished by Mostek in this publication is believed to be accurate and reliable. However, no responsibility is assumed by Mostek for its use; nor for any infringements of patents or other rights of third parties resulting from its use. No license is granted under any patents or patent rights of Mostek. The "PRELIMINARY" designation on a Mostek data sheet indicates that the product is not characterized. The specifications are subject to change, are based on design goals or preliminary part evaluation, and are not guaranteed. Mostek Corporation or an authorized sales representative should be consulted for current information before using this product. No responsibility is assumed by Mostek for its use; nor for any infringements of patents and trademarks or other rights of third parties resulting from its use. No license is granted under any patents, patent rights, or trademarks of Mostek. Mostek reserves the right to make changes in specifications at any time and without

PRINTED IN USA October 1980 STD No. 14819

notice.

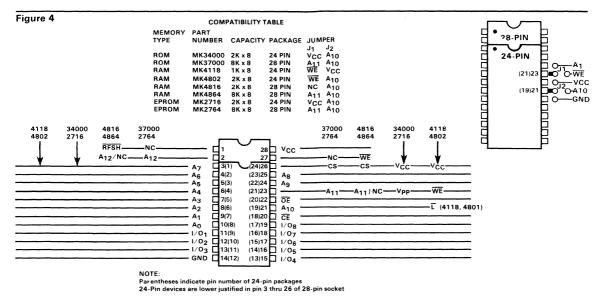

| Memory Type | Part Number   | Capacity  | Package | Jumper |

|-------------|---------------|-----------|---------|--------|

|             |               |           | ı       | 11     |

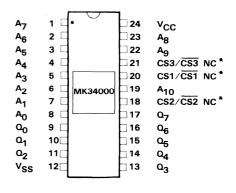

| ROM         | MK34000       | 2K×8      | 24 Pin  | NC     |

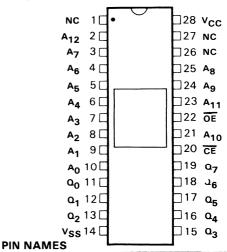

| ROM         | MK37000       | 8K × 8    | 28 Pin  | A11    |

| ROM         |               | 32K × 8 △ | 28 Pin  | A11    |

| RAM         | MK4802        | 2K × 8    | 24 Pin  | WE     |

| RAM         |               | 4K × 8 △  | 28 Pin  | A11    |

| RAM         | MK4118A/4801A | 1K × 8    | 24 Pin  | WE     |

| EPROM       | MK2716        | 2K × 8    | 24 Pin  | VCC    |

| EPROM       | MK2764 △      | 8K × 8    | 28 Pin  | A11    |

△ available 1981

|     |         |        |        | OA11           | O' O∙we | O                |              |        |        |        |                   |        |        |   |

|-----|---------|--------|--------|----------------|---------|------------------|--------------|--------|--------|--------|-------------------|--------|--------|---|

| ہا  | ;<br>][ |        | г<br>З | <sup>2</sup> 2 | ۵       | $\Box_{\approx}$ | $\bar{\Box}$ | ۵<br>۵ | Ω̈́    | Ē      | $\overline{\Box}$ | Ē      | п      | 7 |

| 5   |         | (24)26 | (23)25 | (22) <b>24</b> | (21)23  | (20)55           | (19)21       | (18)20 | (17)19 | (16)18 | (15)17            | (14)16 | (13)15 |   |

| ۽ ا | ٠ ,     | 3(1)   | 4(2)   | 5(3)           | 6(4)    | 7(5)             | (9)8         | (7)    | 10(8)  | 11(9)  | 12(10)            | 13(11) | 14(12) |   |

| T   | JL      |        |        | Ц              | Ш       | П                | П            | П      | П      |        |                   | П      | П      | _ |

|     |         |        |        |                |         |                  |              |        |        |        |                   |        |        |   |

|     |         |        |        |                |         |                  |              |        |        |        |                   |        |        |   |

| 4118/A | 4118/A 4802 | 34000 | 2716 | 4K×8 | 37000 | 32K × 8 2764 | 2764     |             |        | 2764     | 32K × 8 37000 | 37000 | 4K×8 | 2716 | 34000 | 4802 | 4118A |

|--------|-------------|-------|------|------|-------|--------------|----------|-------------|--------|----------|---------------|-------|------|------|-------|------|-------|

| 4801A  |             |       |      | 0    | 0     |              |          |             | ۲      | 0        |               | 0     | 0    |      |       |      | 4801A |

|        |             |       |      | S    | S     | A14          | S        | -           | <br>8  | သသ       | 222           | ၁     | သ    |      |       |      |       |

|        |             |       |      | NC   | A12   | A12          | A12      | 2           | 27     | NC       | NC            | NC    | WE   |      |       |      |       |

| A7     | A7          | A7    | A7   | A7   | A7    | A7           | A7       | 3(1)        | (24)26 | NC<br>NC | A13           | NC    | NC   | VCC  | VCC   | VCC  | VCC   |

| A6     | A6          | A6    | A6   | A6   | A6    | A6           | Pe □     | 4(2) (23)   | (23)25 | A8       | A8            | A8    | A8   | A8   | A8    | A8   | A8    |

| A5     | A5          | A5    | A5   | A5   | A5    | A5           | A5       | 5(3) (22)   | (22)24 | A9       | A9            | A9    | A9   | A9   | A9    | A9   | A9    |

| A4     | <b>A</b> 4  | A4    | A4   | A4   | A4    | A4           | A4       | 6(4) (21)   | (21)23 | A11      | A11           | A11   | A11  | VPP  | Ş     | WE   | WE    |

| A3     | A3          | A3    | A3   | A3   | A3    | A3           | A3       | 7(5) (20)   | (20)22 | O E VPP  | 0 E           | OE    | 0 E  | 0 E  | 0 E   | 0 E  | 0 E   |

| A2     | A2          | A2    | A2   | A2   | A2    | A2           | A2       | 8(6) (19)   | 19)21  |          | A/O           | A10   | A/O  | A10  | A10   | A10  | NC    |

| A1     | A1          | A1    | A1   | A1   | A1    | A1           | A1       | 9(7) (18)   | 18)20  | CE       | CE            | CE    | CE   | CE   | C E   | CE   | CE    |

| Α0     | Α0          | A0    | A0   | A0   | A0    | AO           | ☐<br>0A  | 10(8) (17)  | 17)19  | D7       | D7            | D7    | D7   | D7   | D7    | D7   | D7    |

| 8      | 00          | 00    | D0   | 00   | 00    | 00           | 8        | 11(9) (16)  | 16)18  | D6       | 9G            | D6    | D6   | De   | 90    | De   | 90    |

| 10     | D1          | D1    | D1   | D1   | D1    | D1           | <u>-</u> | 12(10) (15) | (15)17 | D5       | D5            | D5    | D5   | D5   | 50    | D5   | D5    |

| D2     | D2          | D2    | D2   | D2   | D2    | D2           | D2       | 13(11) (14) | (14)16 | D4       | D4            | D4    | D4   | D4   | 04    | D4   | D4    |

| VSS    | VSS         | NSS   | NSS  | VSS  | VSS   | VSS          | VSS      | 14(12) (13) | 13)15  | D3       | D3            | D3    | D3   | 53   | 23    | D3   | D3    |

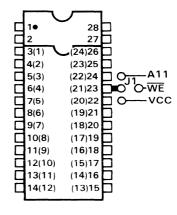

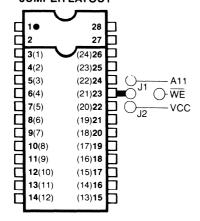

Parenthesis Indicates Pin Number of 24 Pin Packages. 24 Pin Devices are Lower Justified in Pins 3 Thru 26 of 28 Pin Socket

# **TABLE OF CONTENTS**

| e of Contents                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Table of Contents  Numerical Index                                                                                                                   | i                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| eral Information                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Mostek Profile                                                                                                                                       | V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| lication Notes                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Design Memory Boards for RAM/ROM/EPROM Interchange                                                                                                   | . 29<br>. 33<br>. 43                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| a Sheets                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| MK4118A(P/J/N) Series MK4801A(P/J/N) Series MK4802(P/J/N) Series MK4802(P/J/N)-1/3 MK2716(J)-5/6/7/8 MK2764(T)-8 MK34000(P/J/N)-3 MK37000(P/J/N)-4/5 | 71<br>77<br>83<br>89<br>95                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                                                                                                                                                      | Table of Contents. Numerical Index.  Peral Information  Mostek Profile Sales Offices  Designing Microprocessor Memory with Mostek's BYTEWYDE Concept Design Memory Boards for RAM/ROM/EPROM Interchange NMOS RAM Offers Non-Volatility with DATASAVETM  MK4801A/MK4802 For High Speed Aplications Mostek's BYTEWYDE Memory Products  I Sheets  MK4118A(P/J/N) Series MK4801A(P/J/N) Series MK4801A(P/J/N) Series MK4802(P/J/N) Series MK4802(P/J/N) Series MK4802(P/J/N)-1/3 MK2716(J)-5/6/7/8 MK48764(T)-8 MK42000(P/J/N)-3 |

# **NUMERICAL INDEX**

| MK2716(J)-5/6/7/8     | . 89 |

|-----------------------|------|

| MK2764(T)-8           | . 95 |

| MK4118A(P/J/N) Series | . 65 |

| MK4801A(P/J/N) Series | . 71 |

| MK4802(P/J/N) Series  | . 77 |

| MK4802(P/J/N)-1/3     | . 83 |

| MK34000(P/J/N)-3      | . 97 |

| MK37000(P/J/N)-4      | 101  |

# **Mostek - Technology For Today And Tomorrow**

### **TECHNOLOGY**

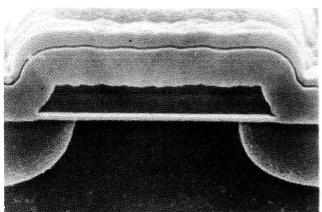

From the beginning, Mostek has been recognized as an innovator. In 1970, Mostek developed the MK4006 1K dynamic RAM and the world's first single-chip calculator circuit, the MK6010. These technical breakthroughs proved the benefits of ion-implantation and cost-effectiveness of MOS. Now, Mostek represents one of the industry's most productive bases of MOS/LSI technology. Each innovation - in memories, microcomputers and telecommunications - adds to that technological capability.

# QUALITY

The worth of a Mostek product is measured by its quality. How well it's designed, manufactured and tested. How well it works in your system.

In design, production and testing, our goal is meeting the spec every time. This goal requires a strict discipline, both from the company and from the individual. This discipline, coupled with a very personal pride, has driven Mostek to build in quality at every level, until every product we take to the market is as well-engineered as can be found in the industry.

# PRODUCTION CAPABILITY

Mostek's commitment to increasing

production capability has made us the world's largest manufacturer of dynamic RAMs. In 1979 we shipped 25 million 4K and 16K dynamic RAMs. We built our first telecommunication tone dialer in 1974; since then, we've shipped over 5 million telecom circuits. The MK3870 single-chip microprocessor is also a large volume product with over two million in application around the world. To meet the demand for our products, production capability must be constantly increased. To accomplish this, Mostek has been in a constant process of expanding and refining our production capabilities.

# THE PRODUCTS

# Telecommunications and Industrial Products

Mostek has made a solid commitment to telecommunications with a new generation of products, such as Integrated Pulse Dialers, Tone Dialers, CODECs, monolithic filters, tone receivers, A/D converters and counter time-base circuits.

Since 1974 over five million telecom circuits have been shipped, making Mostek the leading supplier of tone/pulse dialers and CODECs.

# **Memory Products**

Through innovations in both circuit

design, wafer processing and production, Mostek has become the industry's leading supplier of memory products.

An example of Mostek leadership is our new BYTEWYDE™ family of static RAMs, ROMs, and EPROMs. All provide high performance, N words x 8-bit organization and common pin configurations to allow easy system upgrades in density and performance. Another important product area is fast static RAMs. With major advances in technology, Mostek static RAMs now feature access times as low as 55 nanoseconds. With high density ROMs and PROMs, static RAMs, dynamic RAMs and pseudostatic RAMs, Mostek now offers one of industry's broadest and most versatile memory families.

# **Microcomputer Components**

Mostek's microcomputer components are designed for a wide range of applications.

Our Z80 family is the highest performance 8-bit microcomputer available today. The MK3870 family is one of the industry's most popular 8-bit single-chip microcomputers, offering upgrade options in ROM, RAM, and I/O, all in the same socket. The MK3874 EPROM version supports and prototypes the entire family.

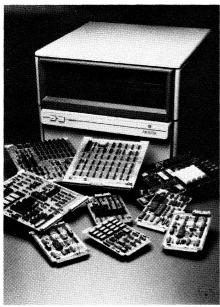

# **Microcomputer Systems**

Supporting the entire component product

line is the powerful MATRIX™ micro-computer development system, a Z80-based, dual floppy-disk system that is used to develop and debug software and hardware for all Mostek microcomputers.

A software operating system, FLP-80DOS, speeds and eases the design cycle with powerful commands. BASIC, FORTRAN, and PASCAL are also available for use on the MATRIX.

Mostek's MD Series™ features both standalone microcomputer boards and expandable microcomputer boards. The expandable boards are modularized by function, reducing system cost because the designer buys only the specific functional modules his system requires. All MDX boards are STD-Z80 BUS compatible.

The STD-Z80 BUS is a multi-sourced motherboard interconnect system designed to handle any MDX card in any card slot.

# **Memory Systems**

Taking full advantage of our leadership in memory components technology, Mostek Memory Systems offers a broad line of products, all with the performance and reliability to match our industry-standard circuits. Mostek Memory Systems offers add-in memory boards for popular DEC and Data General minicomputers.

Mostek also offers special purpose and custom memory boards for special applications.

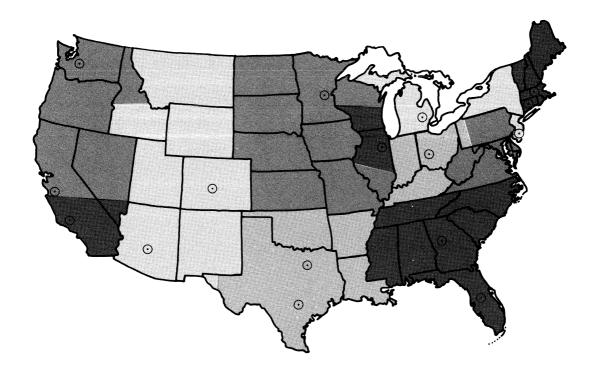

# U.S. AND CANADIAN SALES OFFICES

# CORPORATE HEADQUARTERS

Mostek Corporation 1215 W. Crosby Rd. P. O. Box 169 Carrollton, Texas 75006

### REGIONAL OFFICES Eastern U.S./Canada

Mostek 34 W. Putnam, 2nd Floor Greenwich, Conn. 06830 203/622-0955 TWX 710-579-2928

Northeast U.S. Nostek 29 Cummings Park, Suite #426 Woburn, Mass. 01801 617/935-0635 TWX 710-348-0459

Mid-Atlantic U.S.

Mostek

East Gate Business Center

125 Gaither Drive. Suite D

Mt. Laurel, New Jersey 08054

609/235-4112 TWX 710-897-0723

Southeast U.S. Mostek Exchange Bank Bldg. 1111 N. Westshore Blvd. Suite 414 Tampa, Florida 33607 813/876-1304 TWX 810-876-4611

Atlanta Region 2 Exchange Pl. 2300 Peachford Rd. #2105 Atlanta, GA 30338 404/458-7922 TWX 812-757-4231

Central U.S. Mostek 701 E. Irving Park Road 701 E. Irving Park Ro Suite 206 Roselle, III. 60172 312/529-3993 TWX 910-291-1207

North Central U.S. Mostek 6125 Blue Circle Drive, Suite A Minnetonka, Mn. 55343 612/935-4020 TWX 910-576-2802 South Central U.S.

South Central U.S. Mostek 3400 S. Dixie Ave. Suite 101 Kettering, Ohio 45439 513/299-3405 TWX 810-473-2976

Michigan Mostek Livonia Pavillion East 29200 Vassar, Suite 520 Livonia, Mich. 48152 313/478-1470 TWX 810-242-2978

Southwest U.S. Mostek 4100 McEwen Road Suite 237 Dallas, Texas 75234 214/386-9141 TWX 910-860-5437

South Texas Chevy Chase #4 7715 Chevy Chase Dr., #116 Austin, TX 78752 512/458-5226 TWX 910-874-2007

Northern California Mostek 1762 Technology Drive Suite 126 San Jose, Calif. 95011 408/287-5081 TWX 910-338-7338

Southern California Mostek 18004 Skypark Circle Suite 140 Irvine, Calif. 92714 714/549-0397 TWX 910-595-2513

Rocky Mountains Mostek 8686 N. Central Ave. Suite 126 Phoenix, Ariz. 85020 602/997-7573 TWX 910-957-4581

Denver Region 3333 Quebec, #9090 Denver, CO 80207 303/321-6545 TWX 910-931-2583

Northwest Northwest Mostek 1107 North East 45th Street Suite 411 Seattle, Wa. 98105 206/632-0245 TWX 910-444-4030

# U.S. AND CANADIAN REPRESENTATIVES

ALABAMA

Beacon Elect. Assoc., Inc. 11309 S. Memorial Pkwy. Suite G Suite G Huntsville, AL 35803 205/881-5031 TWX 810-726-2136

ARIZONA

Summit Sales 7336 E. Shoeman Lane Suite 116E Suite 116E Scottsdale, AZ 85251 602/994-4587 TWX 910-950-1283

ARKANSAS Beacon Elect. Assoc., Inc. P.O. Box 5382, Brady Station Little Rock, AK 72215 501/224-5449 TWX 910-722-7310

CALIFORNIA

Harvey King, Inc. 8124 Miramar Road San Diego, CA 92126 714/566-5252 TWX 910-335-1231

COLORADO

Waugaman Associates 4800 Van Gordon Wheat Ridge, CO 80033 303/423-1020 TWX 910-938-0750

CONNECTICUT New England Technical Sales 240 Pomeroy Ave. Meriden, CT 06450 203/237-8827

Carlson Electronic Sales\* 600 East Higgins Road Elk Grove Village, IL 60007 312/956-8240 TWX 910-222-1819

INDIANA Rich Electronic Marketing\* 599 Industrial Drive Carmel, IN 46032 317/844-8462 TWX 810-260-2631

Rich Electronic Marketing 3448 West Taylor St. Fort Wayne, IN 46804 219/432-5553 TWX 810-332-1404

IOWA Cahill, Schmitz & Cahill, Inc. 208 Collins Rd. N.E. Suite K Cedar Rapids, IA 52402 319/377-8219 TWX 910-525-1363

Carlson Electronics 204 Collins Rd. NE Cedar Rapids, IA 52402 319/377-6341 TWX 910-222-1819

KANSAS

Rush & West Associates\* 107 N. Chester Street Olathe, KN 66061 913/764-2700 TWX 910-749-6404

KENTUCKY

RENTUCKY Rich Electronic Marketing 5910 Bardstown Road P. O. Box 91147 Louisville, KY 40291 502/239-2747 TWX 810-535-3757

MARYLAND

Arbotek Associates 3600 St. Johns Lane Ellicott City, MD 21043 301/461-1323 TWX 710-862-1874

MASSACHUSETTS

New England Technical Sales\* 135 Cambridge Street Burlington, MA 01803 617/272-0434 TWX 710-332-0435

MICHIGAN

Action Components 19547 Coachwood Rd. Riverview, MI 48192 313/479-1242

MINNESUTA Cahill, Schmitz & Cahill, Inc. 315 N. Pierce St. Paul, MN 55104 612/646-7217 TWX 910-563-3737

MISSOURI Rush & West Associates 481 Melanie Meadows Lane Ballwin, MO 63011 314/394-7271

NEW JERSEY Tritek Sales, Inc. 140 Barclay Center

Boute #70 Route #70 Cherry Hill, N.J. 08034 609/429-1551 215/627-0149 (Philadelphia Line) TWX 710-896-0881

NEW MEXICO Waugaman Associates 9004 Menaul N.E.

Suite 7 P. O. Box 14894 Albuquerque, NM 87112 505/294-1437

NEW YORK E R A (Engrg. Rep. Assoc.) One DuPont Street Plainview, NY 11803 516/822-9890 TWX 510-221-1849

Precision Sales Corp. 5 Arbustus Ln., MR-97 Binghamton, NY 13901 607/648-3686

Precision Sales Corp.\* 1 Commerce Blvd. Liverpool, NY 13088 315/451-3480 TWX 710-545-0250

Precision Sales Corp. 3594 Monroe Avenue Rochester, NY 14534 716/381-2820

OHIO Rich Electronic Marketing 7221 Taylorsville Road Dayton, Ohio 45424 513/237-9422 TWX 810-459-1767

Rich Electronic Marketing 141 E. Aurora Road Northfield, Ohio 44067 216/468-0583 TWX 810-427-9210

OREGON

OREGON

Northwest Marketing Assoc.

9999 S.W. Wilshire St.

Suite 124

Portland OR 97225

503/297-2581

TELEX 36-0465 (AMAPORT PTL)

TENNESSEE

TENNESSEE

Rich Electronic Marketing

1128 Tusculum Blvd.

Suite D

Greenville, TN 37743

615/639-3139

TWX 810-576-4597

TEXAS

Southern States Marketing, Inc. 14330 Midway Road, Suite 226 Dallas, Texas 75234 214/387-2489 TWX 910-860-5732

Southern States Marketing, Inc. 9730 Town Park Drive, Suite 104 Houston, Texas 77036 713/988-0991 TWX 910-881-1630

HATU

Waugaman Associates 2520 S. State Street #224 Salt Lake City, UT 84115 801/467-4263 TWX 910-925-4026

WASHINGTON Northwest Marketing Assoc. 12835 Bellevue-Redmond Rd. Suite 203E Bellevue, WA 98005 206/455-5846 TWX 910-443-2445

WISCONSIN

Carlson Electronic Sales Northbrook Executive Ctr. 10701 West North Ave. Suite 209 Suite 209 Milwaukee, WI 53226 414/476-2790 TWX 910-222-1819

CANADA

Cantec Representatives Inc.\* 1573 Laperriere Ave. Ottawa, Ontario Canada K1Z 7T3 613/725-3704 TWX 610-562-8967 Cantec Representatives Inc. Cantec Representatives inc. 83 Galaxy Blvd., Unit 1A (Rexdale) Toronto, Canada M9W 5X6 416/675-2460 TWX 610-492-2655

# U.S. AND CANADIAN DISTRIBUTORS

ARIZONA Kierulff Electronics 4134 E. Wood St. Phoenix, AZ 85040 602/243-4101 WW 910/951-1550 Wyle Distribution Group 8155 North 24th Avenue Phoenix, Arizona 85021 602/249-2232 TWX 910/951-4282

CALIFORNIA Bell Industries 1161 N. Fair Oaks Avenue Sunnyvale, CA 94086 408/734-8570 TWX 910/339-9378 Arrow Electronics 521 Weddell Dr. Sunnyvale, CA 94086 408/745-6600 TWX 910/339-9371 Kierulff Electronics 2585 Commerce Way Los Angeles, CA 90040 213/725-0325 TWX 910/580-3106 Kierulff Electronics 8797 Balboa Avenue San Diego, CA 92123 714/278-2112 TWX 910/335-1182 Kierulff Electronics 14101 Franklin Avenue Tustin CA 92680 714/731-5711 TWX 910/595-2599 Schweber Electronics 17811 Gillette Avenue Irvine, CA 92714 714/556-3880 TWX 910/595-1720 Wyle Distribution Group 124 Maryland Street El Segundo, CA 90245 213/322-8100 TWX 910/348-7111 Wyle Distribution Group 9525 Chesapeake Drive San Diego, CA 92123 714/565-9171 TWX 910/335-1590 Wyle Distribution Group 17872 Cowan Ave. Irvine, CA 92714 714/641-1600 TWX 910/348-7111 Wyle Distribution Group 3000 Bowers Ave. Santa Clara, CA 95051 408/727-2500 TWX 910/338-0296

COLORADO Kierulff Electronics 10890 E. 47th Avenue Denver, CO 80239 303/371-6500 TWX 910/932-0169 Wyle Distribution Group 451 E. 124th Ave. Thornton, CO 80241 303/457-9953 TWX 910/936-0770 CONNECTICUT

Arrow Electronics

12 Beaumont Rd.

Wallingford, CT 06492

203/265-7741

TWX 710/476-0162

Schweber Electronics

Finance Drive

Commerce Industrial Park

Danbury, CT 06810

203/792-3500

TWX 710/456-9405

FLORIDA Arrow Electronics 1001 NW 62nd St. Suite 108 Ft. Lauderdale, FL 33309 306.776-7790 TWX 510/955-9456 Arrow Electronics 115 Paim Bay Road, N.W. Suite 10 Bidg. 200 Paim Bay, FL 32905 305.725-1480 TWX 510/959-6337 Diplomat Southland 2120 Calume 1210 Calume 1210 Calume 1313/443-451 TWX 510/959-6336 Kierulff Electronics 3247 Tech Drive St. Petersburg, FL 33702 813/576-1966

GEORGIA Arrow Electronics 2979 Pacific Ave. Norcross, GA 30071 404-/449-8252 TWX 810-/766-0439 Schweber Electronics 4126 Pleasantdale Road Atlanta, GA 30340 404-/449-9170

ILLINOIS Arrow Electronics 492 Lurr Avenue P. O. Box 94248 Schaumburg. IL 60193 312/893-9420 TWX 910/291-3544 Bell Industries 3422 W. Touthy Avenue Chicago, IL 60645 312/982-9210 TWX 910/223-4519 Kierulff Electronics 1536 Lanmeier Elk Grove Village, IL 60007 312/640-0200 TWX 910/223-351 INDIANA Advent Electronics 8446 Moller Indianapolis, IN 46268 317/297-4910 TWX 810/341-3228 Ft. Wayne Electronics 3606 E. Maumee Ft. Wayne, IN 46803 219/423-3422 TWX 810/332-1562 Pioneer/Indiana 6408 Castleplace Drive Indianapolis, IN 46250 317/849-7300 TWX 810/260-1794

IOWA

Advent Electronics

682 58th Avenue

Court South West

Cedar Rapids, IA 52404

319/363-0221

TWX 910/525-1337

MASSACHUSETTES

MASSACHUSETTES Kierulff Electronics 13 Fortune Drive Billerica, MA 01821 617/935-6134 Lionex Corporation 1 North Avenue Burlington, MA 01803 617/272-9400 TWX 710/332-1387 Schweber Electronics 25 Wiggins Avenue Bedford, MA 0132 617/275-61070 07 WX 710/326-0268 Arrow Electronics 95D Commerce Way Woburn, MA 01801 617/933-8130 MARYLAND Arrow Electronics 4801 Benson Avenue Baltimore, MD 21227 301/247-5200 TWX 710/236-9005 Schweber Electronics 9218 Gaither Rd. Gaithersburg, MD 20760 301/840-5900 TWX 710/828-9749

MICHIGAN Arrow Electronics 3810 Varsity Drive Ann Arbor, MI 48104 313/971-8220 TWX 810/223-6020 Schweber Electronics 33540 Schoolcraft Road Livonia, MI 48150 313/625-8100 TWX 810/242-2983

MINNESOTA Arrow Electronics 5251 W. 73rd Street Edina, MN 56435 612. 430-1800 TWX 910/576-3125 Industrial Components 5229 Edina Industrial Blvd. Minneapolis, MN 55435 612/831-2666 TWX 910/576-3153 MISSOURI Olive Electronics 9910 Page Blvd. 5t. Louis, MO 63132 314/426-4500 TWX 910/763-0720 Semiconductor Spec 3805 N. Oak Trafficway Kansas Citry, MO 64116 816/452-3900

NEW HAMPSHIRE Arrow Electronics 1 Perimeter Rd. Manchester, NH 03103 603/668-6968 TWX 710/220-1684

NEW JERSEY Arrow Electronics Pleasant Valley Avenue Morrestown, NJ 08057 609/235-1900 TWX 710/897-0829 Arrow Electronics 285 Midland Avenue Saddlebrook, NJ 07662 201/797-5800 TWX 710/988-2206 Kierufff Electronics 3 Edison Place Fairfield, NJ 07006 201/257-6750 TWX 710/734-4372 Schweber Electronics 18 Madison Road Fairfield, NJ 07006 201/227-7880 TWX 710/734-4305

# U.S. AND CANADIAN DISTRIBUTORS

**NEW MEXICO** Bell Industries 11728 Linn N.E Albuquerque, NM 87123 505/292-2700 TWX 910/989-0625 Arrow Electronics 2460 Alamo Ave. S.E. Albuquerque, NM 87106 505/243-4566 TWX 910/989-1679

**NEW YORK** Arrow Electronics 900 Broad Hollow Rd. Farmingdale, L.I., NY 11735 516/694-6800 TWX 510/224-6494 Arrow Electronics 7705 Maltlage Drive P. O. Box 370 Liverpool, NY 13088 315/652-1000 TWX 710/545-0230 Arrow Electronics 3000 S. Winton Road Rochester, NY 14623 716/275-0300 TWX 510/253-4766 Arrow Electronics 20 Oser Ave. Hauppauge, NY 11787 516/231-1000 TWX 510/227-6623 Lionex Corporation 400 Oser Ave. Hauppauge, NY 11787 516/273-1660 TWX 510/221-2196 Schweber Electronics 2 Twin Line Circle Rochester, NY 14623 716/424-2222 Schweber Electronics Jericho Turnpike Westbury, NY 11590 516/334-7474 TWX 510/222-3660

NORTH CAROLINA Arrow Electronics 938 Burke St. Winston Salem, NC 27102 919/725-8711 TWX 510/931-3169 Hammond Electronics 2923 Pacific Avenue Greensboro, NC 27406 919/275-6391 TWX 510/925-1094

OHIO Arrow Electronics 7620 McEwen Road Centerville, OH 45459 513/435-5563 TWX 810/459-1611 Arrow Electronics 10 Knoll Crest Drive Reading, OH 45237 513/761-5432 TWX 810/461-2670 Arrow Electronics 6238 Cochran Road Solon, OH 44139 216/248-3990 TWX 810/427-9409 Schweber Electronics 23880 Commerce Park Road Beachwood, OH 44122 216/464-2970 TWX 810/427-9441 Pioneer/Cleveland 4800 East 131st Street Cleveland, OH 44105 215/587-3600 TWX 810/422-2211 Pioneer/Dayton-Industrial 4433 Interpoint Blvd. Dayton, OH 45424 513/236-9900 TWX 810/459-1622

OREGON Kierulff Electronics 14273 NW Science Park Portland, OR 97229 503/641-9150 TWX 910/467-8753

PENNSYLVANIA Schweber Electronics 101 Rock Road Horsham, PA 19044 215/441-0600 Arrow Electronics 650 Seco Rd. Monroeville, PA 15146 412/856-7000 412/856-7000 Pioneer/Pittsburgh 560 Alpha Drive Pittsburgh, PA 15238 412/782-2300 TWX 710/795-3122

SOUTH CAROLINA Hammond Electronics 1035 Lown Des Hill Rd. Greenville, SC 29602 803/233-4121 TWX 810/281-2233

**TEXAS**

TEXAS

Arrow Electronics

13715 Gamma Road

P.O. Box 401068

Dallas, TX 75240

214/386-7500

TWX 910/860-5377 Ouality Components 10201 McKalla Suite D Austin, TX 78758 512/835-0220 TWX 910/874-1377 Quality Components 4257 Kellway Circle Addison, TX 75001 214/387-4949 TWX 910/860-5459 Quality Components 6126 Westline Houston, TX 77036 713/772-7100 Schweber Electronics 7420 Harwin Drive Houston, TX 77036 713/784-3600 TWX 910/881-1109 UTAH

Bell Industries

3639 W. 2150 South

Salt Lake City, UT 84120

801/972-6969

TWX 910/925-5686 Kierulff Electronics 2121 South 3600 West Salt Lake City, UT 84104 801/973-6913

WASHINGTON Kierulff Electronics 1005 Andover Park East Tukwila, WA 98188 206/575-4420 TWX 910/444-2034 Wyle Distribution Group 1750 132nd Avenue N.E. Bellevue, Washington 98005 206/453-8300 TWX 910/443-2526

WISCONSIN Arrow Electronics 434 Rawson Avenue Oak Creek, WI 53154 414/764-6600 TWX 910/262-1193 Kierulff Electronics 2212 E. Moreland Blvd. Waukesha, WI 53186 414/784-8160 TWX 910/262-3653

Preico Electronics 2767 Thames Gate Drive Mississauga, Ontario Toronto L4T 1G5 416/678-0401 TWX 610/492-8974 Preico Electronics

480 Port Royal St. W.

Montreal 357 P.O. H3L 2B9

514/389-8051

TWX 610/421-3616

Preico Electronics

1770 Westband Princ 1770 Woodward Drive Ottowa, Ontario K2C 0P8 613/226-3491 Telex 05-34301 R.A.E. Industrial 3455 Gardner Court Burnaby, B.C. V5G 4J7 604/291-8866 TWX 610/929-3065 Zentronics 141 Catherine Street Ottawa, Ontario K2P 1C3 613/238-6411 Telex 05-33636 Zentronics Zentronics 1355 Meyerside Drive Mississauga, Ontario (Toronto) L5T 1C9 416/676-9000 Telex 06-983657 Zentronics 5010 Rue Pare Montreal, Quebec M4P 1P3 514/735-5361 Telex 05-827535 Zentronics Zentronics 590 Berry Street St. James, Manitoba (Winnipeg) R2H OR4 204/775-8661 Zentronics 480A Dutton Drive Waterloo, Ontario N2L 4C6 519/884-5700

CANADA

# INTERNATIONAL MARKETING OFFICES

**EUROPEAN HEAD OFFICE**

Mostek International

150 Chaussee de la Hulpe

B-1170 Brussels

Belgium

(32) 2 6606924

Telex - 846 62011 MKRRUR

FRANCE Mostek France S.A.R.L.

30, Rue de Morvan Silic 505 94623 Rungis Cedex (33) 1 6873414

Telex - 842 204049 MKFRANF F

GERMANY

Mostek GmbH Talstrasse 172 Schurwaldstrasse 15 D-7303 Neuhausen/Fildet 7158/66.45 Telev - 72 38 86

Mostek GmbH Friedlandstrasse 1 2085 Quickborn/Hamburg (49) 40 41062077/2078 Telex - 841 1213685 MKHA D Mostek GmbH Zaunkoenigstrasse 18 D-8021 Ottobrunn (49) 89 6091017-19 Telex - 841 5216516 MKMU D

ITALY

Mostek Italia S.P.A.

Via G. da Procida, 10

I-20149 Milano

(39) 2 3185337 or

3492696

Telex - 843 333601 MOSTEK i

JAPAN

Sanyo Bidg 3F 1-2-7 Kita-Aoyama Minato-Ku, Tokyo 107 (81) 3 4047261 \*Telex 781 23686 J23686 MOSJAOY

Mostek Scandinavia AB Magnusvagen 1

S-175 31 Jarfalla (46) 758-343-38 Telex - 854 12997 MOSTEK S UNITED KINGDOM

Mostek U.K. Ltd. Masons House, 1-3 Valley Drive, Kingsbury Road, London, NW9 (44) 1 2049322

Telex - 851 25940 MOSTEK G

# INTERNATIONAL SALES REPRESENTATIVES/DISTRIBUTORS

ARGENTINA

Rayo Electronics S.R.L. Belgrano 990, Pisos 6y2 1092 Buenos Aires (38)-1779, 37-9476 Telex - 122153

**AUSTRALIA**

Amtron Tyree Pty.Ltd. 176 Botany Street Waterloo, N.S.W. 2017 (61) 69-89.666 Telex - 25643

AUSTRIA

Transistor-Vertriebs GmbH Auhofstrasse 41 A A-1130 Vienna (43) 222-829.45.12 Telex - 13738

BRASIL Cosele, Ltd.

Rua da Consolacao, 867 Conj. 31 01301 Sao Paulo (55) 11-257.35.35/258.43.25 Telex - 1130869

BELGIUM

Sotronic 14, Rue Pere de Deken B-1040 Brussels (32) 2-736.10.07 Telex - 25141

DENMARK Semicap APS

Semicap APS Gammel Kongevej 184.5 DK-1850 Copenhagen (45) 1-22.15.10 Telex - 15987

FINLAND

S.W. Instruments Karstulantie 4 B SF-00550 Helsinki 65 (358)-0-73.82.65 Telex - 122411 FRANCE P.E.P.

4, Rue Barthelemy F-92120 Montrouge (33) 1-735.33.20 Telex - 204534

SCAIB 80, rue d'Arcueil SILIC 137 F-94150 Rungis Cedex (33) 1-687.23.12 Telex - 204674

Societe COPEL Rue Fourny - Z.I. B.P. 22 F-78530 BUC 1/956.10.18 Telex - 69.63.79

SORHODIS 150-152, rue Anatole France F-69100 VILLEURBANNE 78/85.00.44 Telex 38.01.81

GERMANY

Neye Enatechnik GmbH Schillerstrasse 14 D-2085 Quickborn (49) 4106-61.21.95 Telex - 213.590

Dr Dohrenberg Bayreuther Strasse 3 D-1 Berlin 30 (49) 30-213.80.43 Telex - 184860

Raffel-Electronic GmbH Lochnerstrasse 1 D-4030 Ratingen (49) 2102-280.24 Telex - 8585180

Siegfried Ecker Koenigsberger Strasse 2 D-6120 Michelstadt (49) 6061-2233 Telex - 4191630

Matronic GmbH Lichtenberger Weg 3 D-7400 Tuebingen (49) 7071/24.331 Telex - 726.28.79

Dema-Electronic GmbH Bluetenstrasse 21 D-8 Muenchen 40 (49) 89-288018 Telex - 28345 HONG KONG

1402 Tung Wah Mansion 199-203 Hennessy Road Wanchai, Hong Kong (5)-72.93.76 Telex - 85148

ISRAEL

Telsys, LTD. 12 Kehilat Venetsia St. Tel Aviv 48.21.26-28 Telex - 32.392

ITALY

Comprel S.r.L. Viale Romagna, 1 I-20092 Cinisello Balsamo (39) 2-928.08.09/928.03.45 Telex - 332484

EMESA S.P.A. Via L. da Viadana, 9 I-20122 MILANO 2/869.06.16 Telex - 33.50.66

JAPAN

Systems Marketing, Inc. 4th Floor, Shindo Bldg. 3-12-5 Uchikanda, Chiyoda-Ku, Tokyo, 100 (81) 3-254.27.51 Telex - 25761

Teijin Advanced Products Corp 1-1 Uchisaiwai-Cho 2-Chome Chiyoda-Ku Tokyo, 100 (81) 3-506.46.73 Telex - 23548

KOREA

Vine Overseas Trading Corp. Room 303-Tae Sung Bldg. 199-1 Jangsa-Dong Jongro-Ku Seoul (26)-1663, 25-9875 Telex - 24154

THE NETHERLANDS Nijkerk Elektronika BV Drentestraat 7 1083 HK Amsterdam (020.) 428. 933

Telex - 11625

NEW ZEALAND

E.C.S. Div. of Airspares P.O. Box 1048 Airport Palmerston North (77)-047 Telex - 3766

NORWAY

Hefro Tekniska A/S Postboks 6596 Rodelkka Oslo 5 (47) 2-38.02.86 Telex - 16205

SINGAPORE

Dynamar International, LTD. Suite 526, Cuppage Center 55 Cuppage Road Singapore 0922 (65) 235-1139 Telex - 786-26283

SOUTH AFRICA Radiokom P.O. Box 56310

P.O. Box 56310 Pinegowrie 2123, Transvaal 789-1400 Telex - 8-0838 SA

SPAIN

Comelta S.A.

Cia Electronica Tecnicas Aplicadas

Consejo de Ciento, 204

Entio 3A.

Barcelona 11

(34) 3-254.66.07/08

Telex - 51934

COMELTA S.A. Cia Electronica Tecnicas Aplicadas Emilio Munoz 41, Esc. 1, Planta 1, Nave 2 Madrid 17 1/754-4530/4621/3077/3001 Telex - 42.007

SWEDEN Interelko AB Strandbergsg. 47 S-11251 Stockholm (46) 8-13,21,60

SWITZERLAND Memotec AG CH-4932 Lotzwil (41) 63-28.11.22 Telex - 68636

Telex - 10689

TAIWAN Dynamar Taiwan Limited

P.O. Box 67-445 2nd Floor, No. 14, Lane 164 Sung-Chiang Road Taipei 5418251

5418251 Telex - 11064

UNITED KINGDOM Celdis Limited 37-39 Loverock Road Reading Berks RG 31 ED (44) 734-58.51.71 Telex - 848370

Distronic Limited 50-51 Burnt Mill Elizabeth Way, Harlow Essex CM 202 HU (44) 279-32.497/39.701 Telex - 81387

A.M. Lock Co., Ltd. Neville Street, Chadderton, Oldham, Lancashire (44) 61-652.04.31 Telex - 669971

Pronto Electronic Systems Ltd. 645 High Road, Seven Kings, Ilford, Essex IG 38 RA (44) 1-599.30.41 Telex - 24507

Pronto Electronic Systems Ltd. 466-478 Cranbrook Road, Gants Hill Illford Essex 1G3 8RA

Essex 1G3 8RA 1/599.30.41 Telex - 24.507

YUGOSLAVIA Chemcolor

Chemcolor Inozemma Zastupstva Proleterskih brigada 37-a 41001 Zagreb (41)-513.911 Telex - 21236

# DESIGNING MICROPROCESSOR MEMORY WITH MOSTEK'S BYTEWYDE CONCEPT

# TABLE OF CONTENTS

|                                                             |                                                                                                                                                | Pag                                                                                                                                                                                                                                                                                                                                                                                                                                 | е                                                                    |

|-------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|

| ı                                                           | Introduction                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                     | 1                                                                    |

| 11                                                          | BYTEWYDE                                                                                                                                       | Control Functions                                                                                                                                                                                                                                                                                                                                                                                                                   | 3                                                                    |

| Ш                                                           | Interfaces to                                                                                                                                  | Popular Microprocessors                                                                                                                                                                                                                                                                                                                                                                                                             | 4                                                                    |

| IV                                                          | Printed Circu                                                                                                                                  | uit Board Example                                                                                                                                                                                                                                                                                                                                                                                                                   | 2                                                                    |

| V                                                           | Microproces                                                                                                                                    | sor Memory Alternatives2                                                                                                                                                                                                                                                                                                                                                                                                            | 5                                                                    |

| Со                                                          | nclusions                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                     | 27                                                                   |

|                                                             |                                                                                                                                                | LIST OF TABLES AND FIGURES                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                      |

|                                                             |                                                                                                                                                | Pag                                                                                                                                                                                                                                                                                                                                                                                                                                 | је                                                                   |

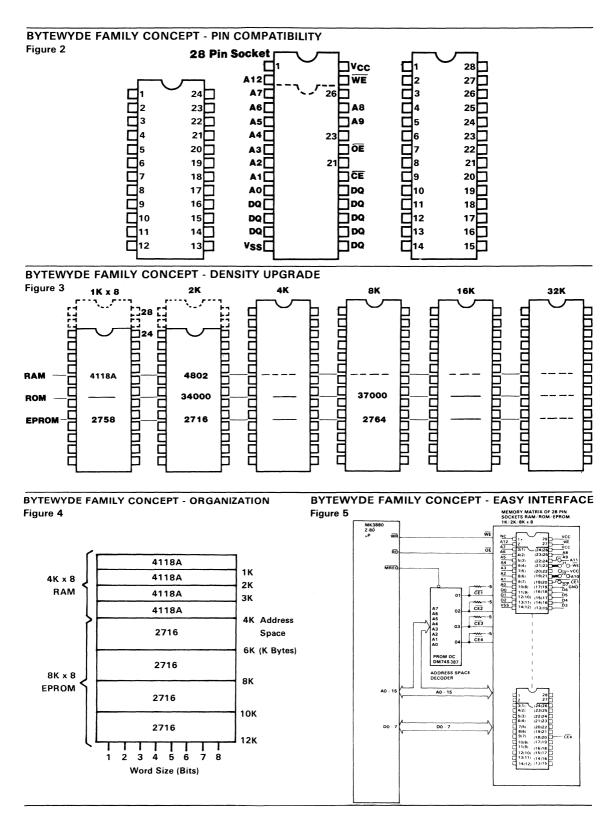

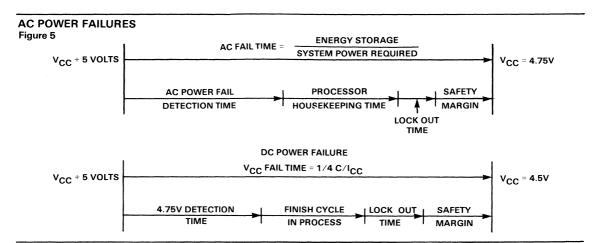

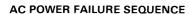

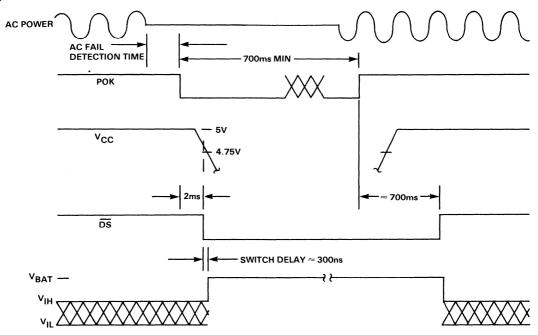

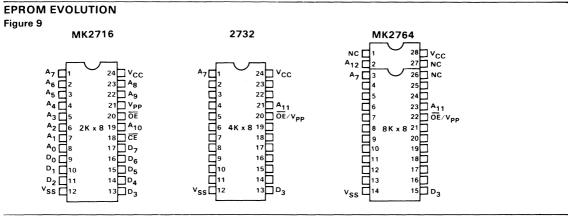

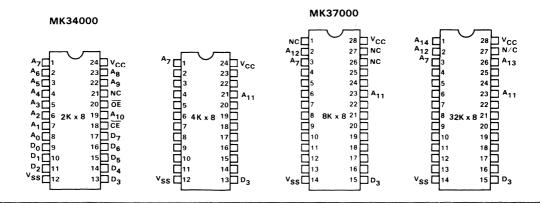

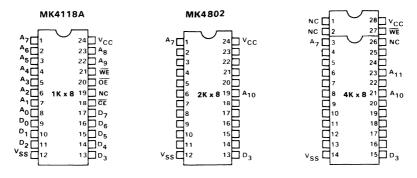

| Fig<br>Fig<br>Fig<br>Fig<br>Fig<br>Fig<br>Ta                | ure 1 ure 2 ure 3 ure 4 ure 5 ure 6 ure 6 ure 7 ure 8 ure 9 ble 1 ble 2                                                                        | BYTEWYDE Family Concept - Interchangeability BYTEWYDE Family Concept - Pin Compatibility BYTEWYDE Family Concept - Density Upgrade BYTEWYDE Family Concept - Organization BYTEWYDE Family Concept - Easy Interface Output Buffer Configurations (Share Bus) Read-Read Bus Contention Write-Read Bus Contention Address-Data Bus Contention Mostek's BYTEWYDE Static Memory Family Memory/Microprocessor Performance Cross Reference | <pre>2 2 2 2 3 3 4 4 5 6</pre>                                       |

| Fig<br>Fig<br>Fig<br>Fig<br>Fig<br>Fig<br>Fig<br>Fig<br>Fig | gure 10, 10A gure 11, 11A gure 12, 12A gure 13, 13A gure 14, 14A gure 15, 15A gure 16, 16A gure 17 gure 18 ble 3 gure 19 gure 20 gure 21 ble 4 | Interface to 3880/Z80 Interface to 6809 Interface to 8085/8088 Interface to 6500 Interface to 6800 Interface to Z8000 Interface to 8086 Printed Board Layout (Solder Side) Circuit Board Layout (Component Side) Parts List Printed Circuit Board Schematic Jumper Layout for Memory Board Layout Space Comparisons Comparative Analysis Table                                                                                      | 10<br>12<br>14<br>16<br>18<br>20<br>22<br>23<br>24<br>24<br>25<br>26 |

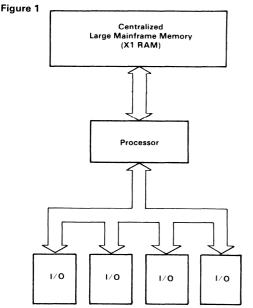

### INTRODUCTION

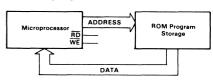

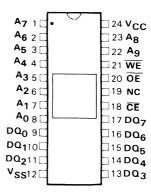

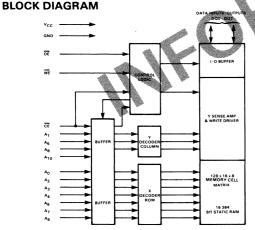

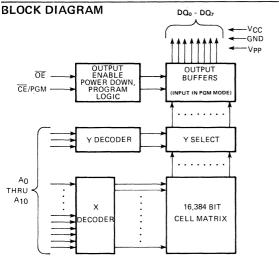

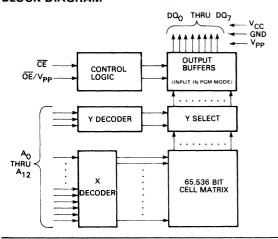

The term "byte wide" refers to a memory element which stores an 8-bit data word (byte) for each address location. Since all microprocessors are byte oriented, byte wide memories are a natural building block for microprocessors.

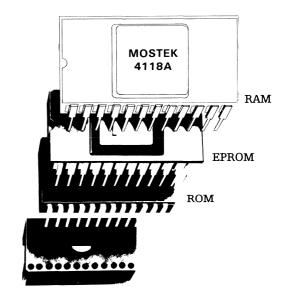

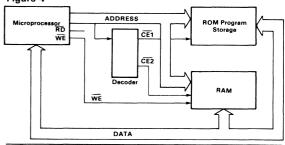

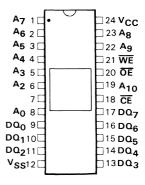

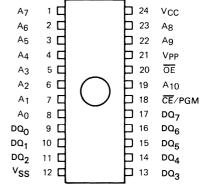

Mostek's BYTEWYDE concept ushers in a new era of compatibility for memory designs. For the first time RAM, ROM, and EPROM can be interchanged in the same socket because they share a common pin out. (Figure 1) Upgradeability is assured by carefully planned next generation devices. This flexibility allows for the design of an obsolescent proof memory system.

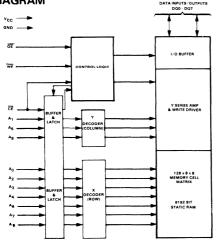

The members of Mostek's BYTEWYDE family feature chip enable  $(\overline{CE})$  and output enable  $(\overline{OE})$  controls to facilitate simple interface to microprocessors and enhance performance. The BYTEWYDE memories can meet the requirements of even the fastest microprocessors.

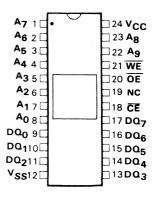

Standard 24 and 28 pin dual-in-line packages were chosen to implement the BYTEWYDE family. To obtain maximum flexibility, a 28 pin socket site can be used to accept both the 24 and 28 pin devices. (Figure 2) The same BYTEWYDE memory design can remain cost effective and density competitive by upgrading to future components of the family. This prolonged product life increases return on the engineering investment and economies to scale. Mostek is committed to pin compatibility between today's memories and future generation devices. (Figure 3)

Interchangeability between RAM, ROM and EPROM is a key issue in Mostek's BYTEWYDE approach. The distinction between these devices is primarily data retention, when viewed from the system level. Therefore, design constraints are removed since early definition of the quantity of RAM versus ROM (EPROM) is not needed. End products are, as a result, more adaptive to changing market needs by substitution of the different memory devices.

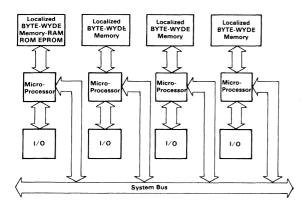

Microprocessor memories using an organization of N words x 8 bits (byte) are an optimum building block. With a trend towards distributed processor architecture, BYTEWYDE memories will have an even more pronounced effect on implementation. In distributed

systems the overall memory required can be large, but the concentration of memory in any one computing element is comparatively small. A typical requirement for a computing element might be 12K bytes. Using BYTEWYDE memories, between 2 and 8 devices would be needed, depending upon the mix of RAM/ROM FPROM.

Substituting the necessary number of 16K or 64K one bit wide memories in this application will quickly show the advantage of the BYTEWYDE approach. (Figure 4)

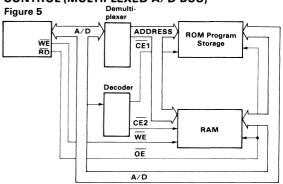

Mostek's BYTEWYDE memories are easy to use. Adequate control functions are provided to minimize interface complexity and enhance performance. The static characteristics of these memories eliminate the need for refresh circuitry. The simplicity of interfacing microprocessors to a Mostek BYTEWYDE memory array has been reduced to merely connecting address, data lines, and control signals. (Figure 5)

# BYTEWYDE FAMILY CONCEPT INTERCHANGEABILITY

Figure 1

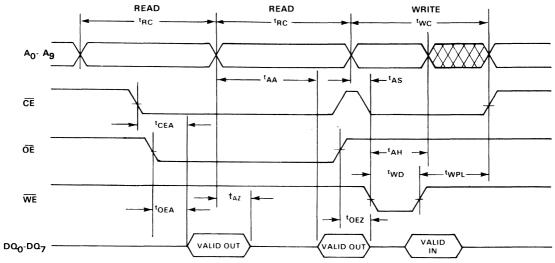

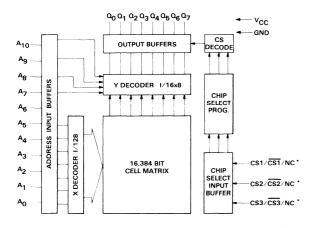

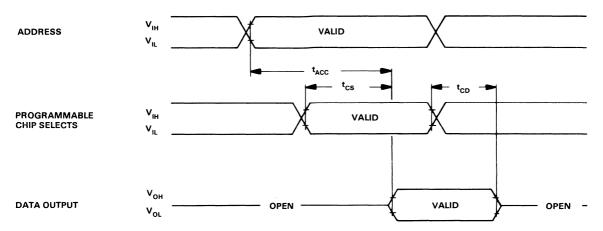

### BYTEWYDE CONTROL FUNCTIONS

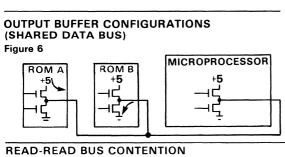

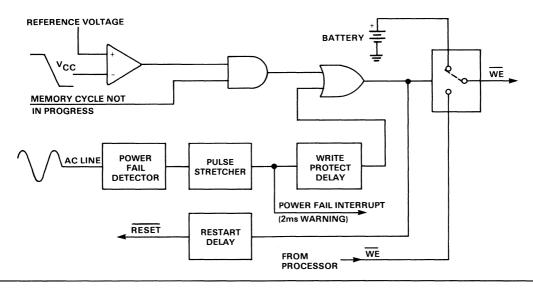

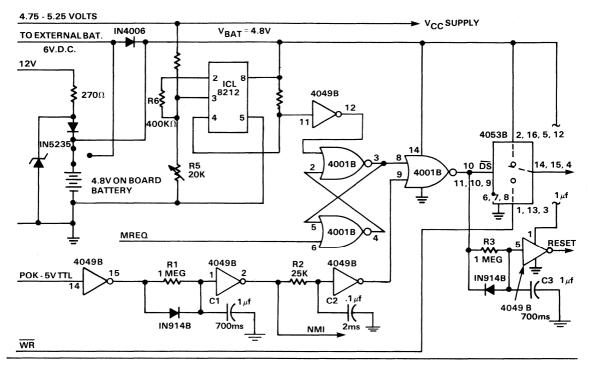

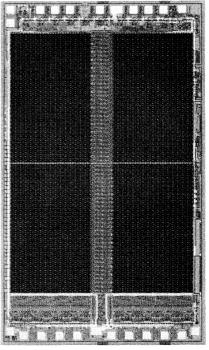

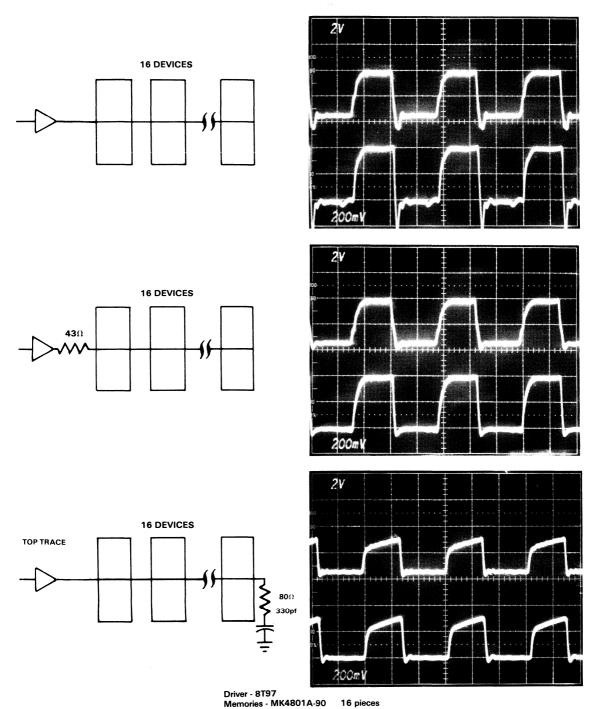

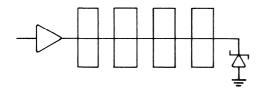

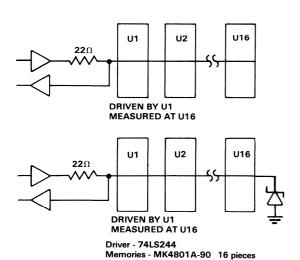

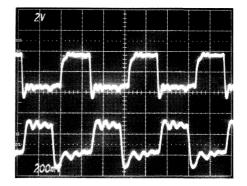

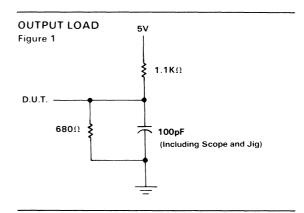

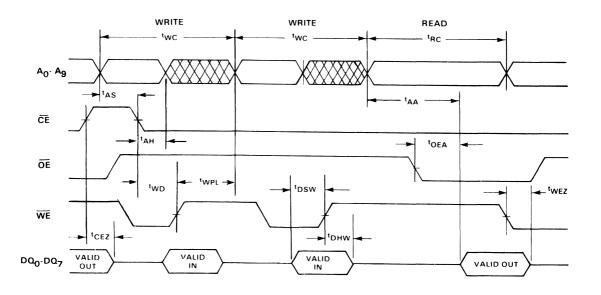

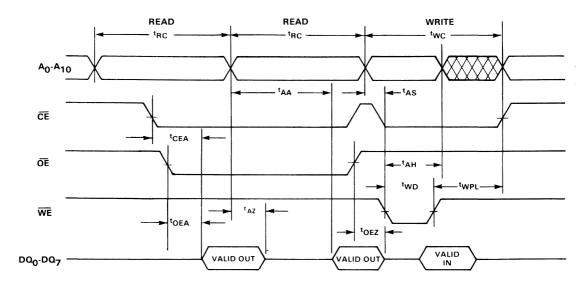

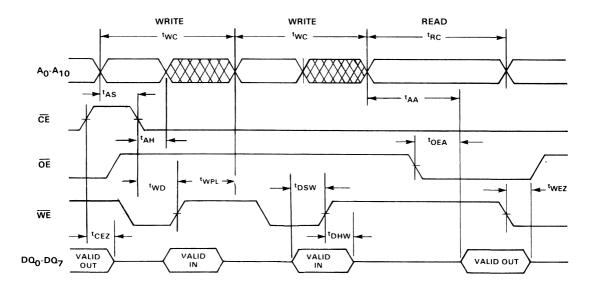

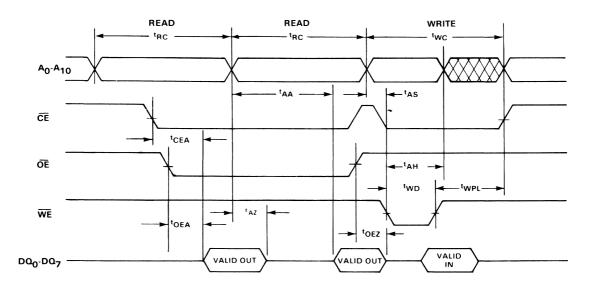

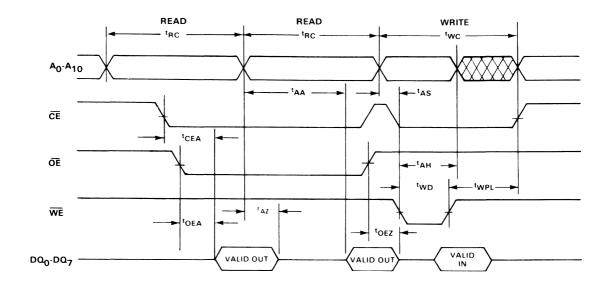

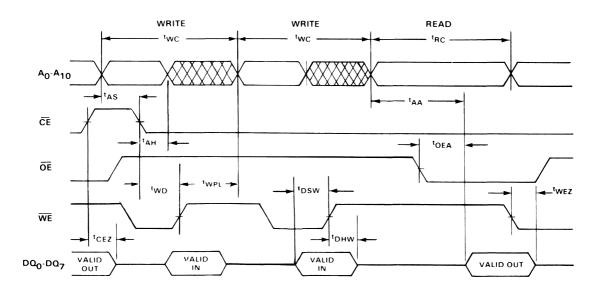

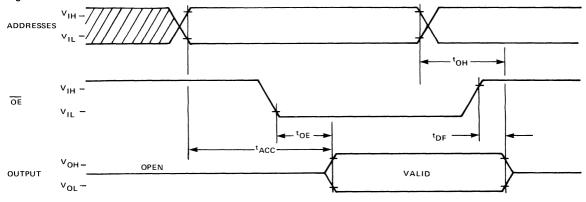

A common difficulty experienced when interfacing memory on a shared data bus as found in a microprocessor system is bus contention. Bus contention is a term used to describe the condition in which two or more output buffers on the same bus line are enabled. These output buffers may reside in different memory devices within an array, peripheral interfaces, microprocessors, or any of the above. If suitable control functions are provided on each memory, data bus timing becomes well defined and the problem goes away without performance degradation.

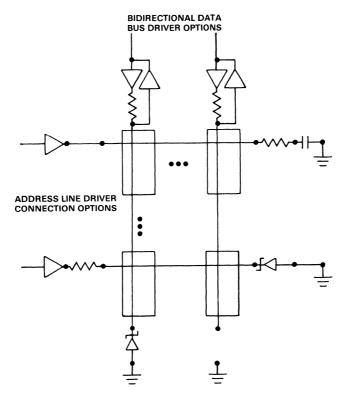

A BYTEWYDE memory provides two control functions so that system performance will not be compromised for lack of output buffer control. Memory busses are commonly constructed with three levels of complexity. In the simplest case the bus has unidirectional data flow. A more complex bidirectional data bus allows data to flow into and out of the memory on the same lines but at different times thus conserving package pins, printed circuit board track, and connectors. To further conserve lines, addresses are sometimes multiplexed with a bidirectional data bus. In any of these cases the system designer must be able to guarantee that for any point in time the bus be defined for data in, data out, or address. In this way bus contention is eliminated.

Bus contention is defined to be a condition when two or more output buffers on the same line are simultaneously turned on.

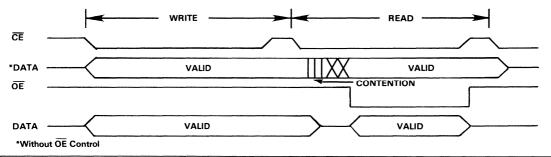

In Figure 6 ROM A and ROM B are said to be in bus contention because A is sourcing current "1" and B is

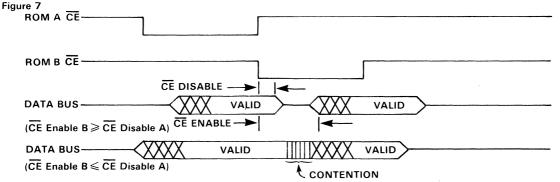

sinking current "O" at the same point in time creating a short circuit across the power supply. For proper system operation ROM A must go to a high impedance state prior to ROM B output turning on. This break before make characteristic is essential for all multi output bus schemes. Short periods of bus contention normally cause no catastrophic damage but do generate large amounts of system noise. This noise can cause an obscure system malfunction which does not lend to straight forward troubleshooting procedures. For reliable system operation bus contention must be avoided. The timing diagram Figure 6 shows ROMA and ROM B implemented with output buffers controlled solely by  $\overline{\text{CE}}$  (chip enable).

In this case the output buffer enable time must be longer than the disable time when switching from A to B to insure a contention free bus; however, this is difficult to achieve in practice because of unit to unit variations among devices. The second data bus waveform shows the contention problem when  $\overline{CE}$  enable B time is less than  $\overline{CE}$  disable A time.

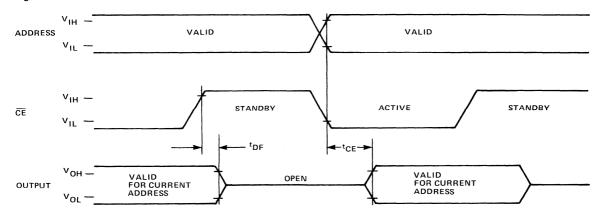

If a fast  $\overline{OE}$  (output enable) control is provided in addition to the  $\overline{CE}$  control no constraints are placed on  $\overline{CE}$  for bus contention. In this way  $\overline{CE}$  is reserved for device selection and  $\overline{OE}$  for buffer control. When a device is given a  $\overline{CE}$  it is singled out in a matrix as the device to go into cycle. The selected device then powers up for the cycle. After the device is selected, at a time when bus contention is not a problem,  $\overline{OE}$  can be used to gate data on and off the bus. This freedom to control the bus with the  $\overline{OE}$  allows the next cycle to be initiated with  $\overline{CE}$  prior to the bus being released from the previous cycle thus enhancing performance or widening operating margin.

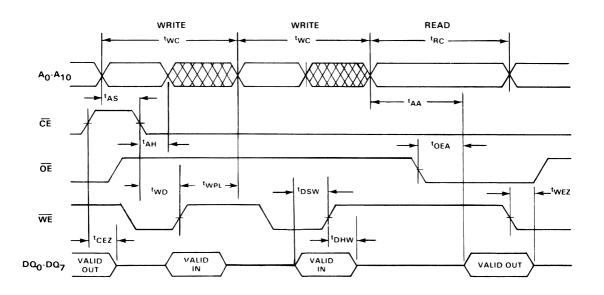

When a bidirectional data bus scheme is configured the possibility of another form of bus contention exists when a write is followed by a read. Typically the data in for a write must be held valid until the completion of the write cycle. During this write time data is flowing into the memory and is being driven by the output of the microprocessor. If a read cycle immediately follows a write cycle the data bus has to switch from data in to data out. If the read device output is solely controlled by

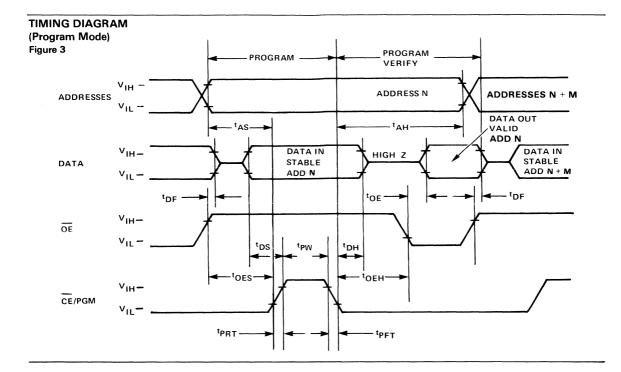

CE the potential exists for the buffer to turn on before the data in (write data) from the microprocessor goes high impedance. The addition of an OE control function would allow the selection and initialization of the read to occur without delay by using OE to gate the read data on the bus after the write data cleared the bus. Figure 8 shows what happens with and without the additional OE control.

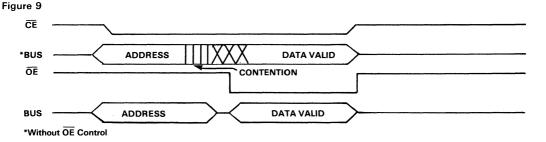

An even more restrictive condition exists when the data bus is bidirectional and address is multiplexed as in the 8085 or 8086 microprocessor. In this case the read cycle first has an address on the bus followed by data, as shown in Figure 9.

With a sole  $\overline{\text{CE}}$  control a fast memory could cause bus contention by sourcing or sinking output current before the bus achieved a high impedance condition from the address state. This contention problem can be resolved without performance degradation by the addition of an  $\overline{\text{OE}}$  as seen in Figure 9.

In short, the addition of the  $\overline{\text{OE}}$  control function on Mostek's BYTEWYDE memories provides the designer with a powerful tool to resolve bus contention problems. Memories without two control functions often result in more restrictive performance or external bus control elements.

# WRITE-READ BUS CONTENTION Figure 8

# **ADDRESS-DATA BUS CONTENTION**

# INTERFACES TO POPULAR MICROPROCESSORS

Microprocessor applications have become pervasive. The ability to replace discrete hardware logic with microprocessor software has been closely coupled with advances in memory technology.

The spectrum ranges from consumer applications where cost and volume availability are paramount to the high performance and/or hi-reliability applications areas where cost is not the greatest concern. The consumer applications include video games, home computers, trip monitors, household controllers, etc.

BYTEWYDE memory has been designed to fit into those applications requiring full utilization of the micro-

processor performance and low cost. It can quite easily be interfaced almost directly to any microprocessor. The Figures, Schematics, and Timing diagrams which follow illustrate this concept.

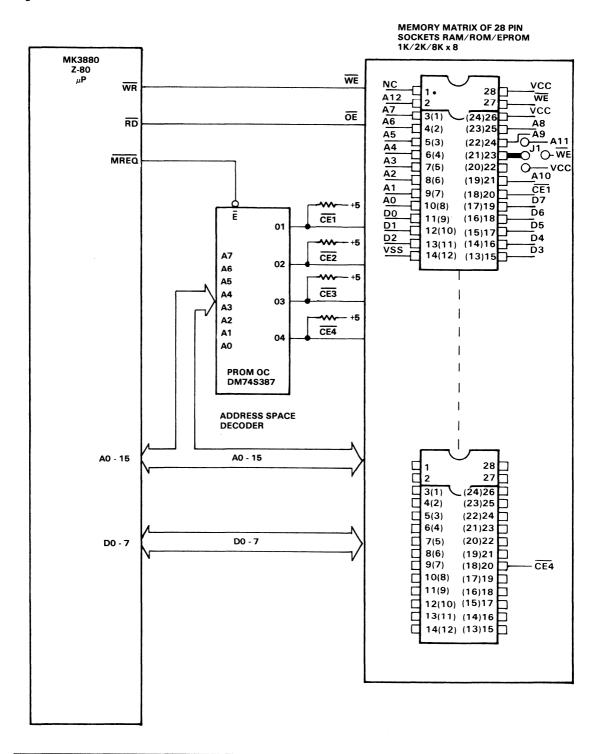

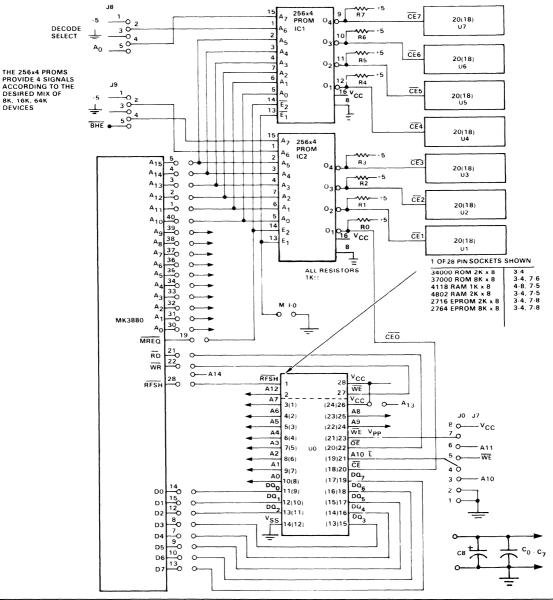

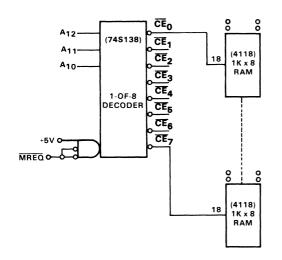

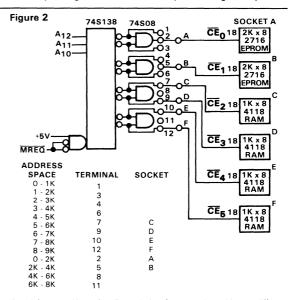

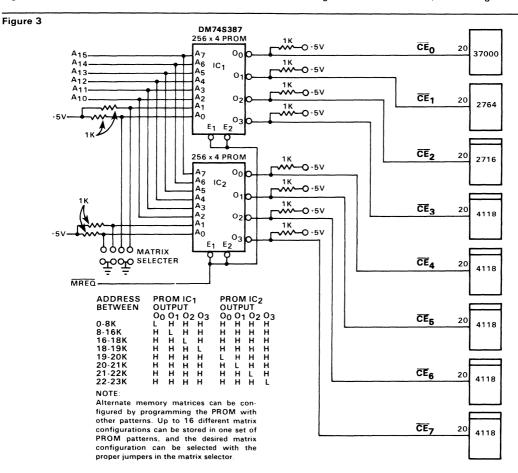

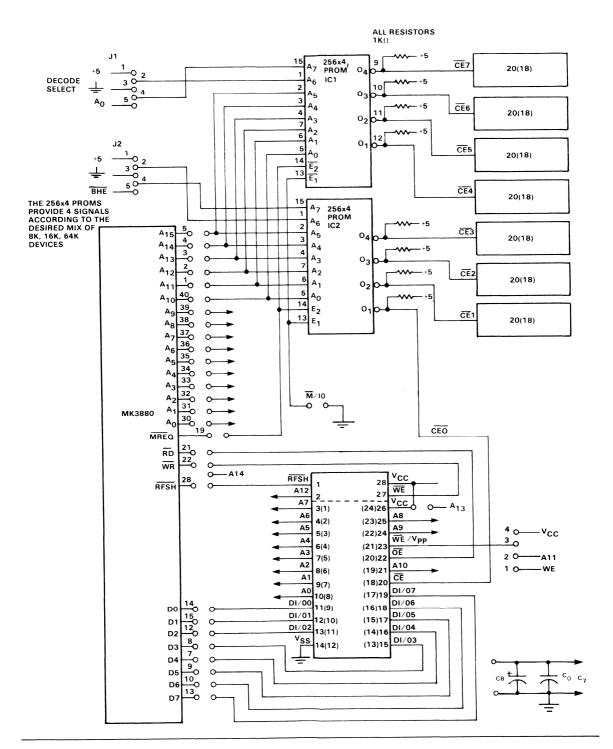

Figure 10 shows how the BYTEWYDE memory may be connected to the very popular present day 8 bit microprocessor MK3880 (Z80). This is a very simple configuration utilizing 28 pin sockets with the capability of using any RAM, ROM, or EPROM memory size. The high order microprocessor address bits are fed to a 74S387 256 x 4 PROM for address space decoding. The PROM allows the address space to be redefined at any time so that various mixes of RAM, ROM or EPROM can be used. The number of jumper connections required to utilize from 1K x 8 to 8K x 8 of PROM, 1K x 8 to 8K x 8 of

# MOSTEK'S BYTEWYDE STATIC MEMORY FAMILY Table 1

| Memory Type | Part Number   | Capacity  | Package | Jumper |

|-------------|---------------|-----------|---------|--------|

| ;           |               | ,         | 1.      | 11     |

| ROM         | MK34000       | 2K×8      | 24 Pin  | NC     |

| ROM         | MK37000       | 8K × 8    | 28 Pin  | A11    |

| ROM         |               | 32K × 8 △ | 28 Pin  | A11    |

| RAM         | MK4802        | 2K × 8    | 24 Pin  | WE     |

| RAM         |               | 4K × 8 △  | 28 Pin  | A11    |

| RAM         | MK4118A/4801A | 1K×8      | 24 Pir  | WE     |

| EPROM       | MK2716        | 2K × 8    | 24 Pin  | vcc    |

| FPROM       | MK2764 △      | 8K × 8    | 28 Pin  | A11    |

I VCC -wE 1 A 11

(19)21

6(4) 7(5) 8(6)

5(3)

13(11) 14(12) 12(10) 11(9) 10(8)

(23)25 (22)24 (21)23 (20)55 (18)20 (17)19 (16)18 (15)17 (14)16 (13)15

(24)26

| 981   |

|-------|

| 198   |

| e     |

| ailab |

| ava   |

| ◁     |

| 4118/A | 4118/A 4802 | 34000 | 2716 | 4K×8 | 37000 | 32K×8 | 2764 |                |                | 2764   | 32K×8 | 32K×8 37000 | 4K×8 2716 | 2716 | 34000 | 4802 | 4118A |

|--------|-------------|-------|------|------|-------|-------|------|----------------|----------------|--------|-------|-------------|-----------|------|-------|------|-------|

| 4801A  | !<br>)<br>) |       |      |      |       |       |      |                | ſ              |        |       |             |           |      |       |      | 4801A |

|        |             |       |      | SC   | NC    | A14   | NC   | )<br>          | 78             | VCC    | VCC   | VCC         | QC<br>VCC |      |       |      |       |

|        |             |       |      | CZ   | A12   | A12   | A12  | ~<br> <br>     | 27             | SC     | S     | SC          | N<br>E    |      |       |      |       |

| 7.4    | 47          | 47    | A7   | A7   | A7    | A7    | A7   |                | (24) <b>26</b> | S      | A13   | NC          | SC        | VCC  | VCC   | VCC  | VCC   |

| Ž V    | Č «         | 2 9   | ΔA   | ΔĠ   | ΔG    | A6    | A6   | 4(2)           | (23)25         | A8     | A8    | A8          | A8        | A8   | A8    | A8   | A8    |

| AO A   | 200         | 2 4   | A5.  | AS   | Δ5    | 45    | A5   | ĵ.             | 42(22)         | A9     | A9    | A9          | A9        | A9   | A9    | A9   | A9    |

| A3     | 2 2         | 2 4   | S 4  | A4   | A4    | A4    | A4   | ][<br>(4)      | (21)23         | A11    | A11   | A11         | A11       | ΛЬР  | SC    | WE   | WE    |

| \$ C   | 43          | Δ3    | A3   | A3   | A3    | A3    | A3   | ][<br>(§)      | (50)           | OE VPP | OE    | OE          | 0 E       | 0 E  | 0 E   | OE   | OE    |

| 2 5    | 5 5         | 42    | A2   | Α2   | Α2    | A2    | A2   | ()<br>()<br>() | 19)21          | A10    | A/O   | A10         | A/O       | A10  | A10   | A10  | NC    |

| A2     | 7 7         | 2 2   | Δ1   | 41   | Δ1    | A1    | Α1   | ][<br>][       | 18)20          | CE     | CE    | CE          | CE        | CE   | CE    | CE   | CE    |

| T 4    | 2 2         | 2     | AO A | 00   | Φ     | AO    | AO   | عال            | 15.5<br>11.00  | D7     | 10    | 107         | D7        | 07   | D7    | D7   | D7    |

| 2 2    | 2 2         | 2 2   | 2 2  | 2 2  | 2 2   | 2 00  | 00   | JL<br>6        | 16)18          | 90     | 90    | 90          | 90        | 90   | 90    | D6   | D6    |

| 3 2    | 8 2         | 3 2   | 2 2  | 10   | 10    | 01    | 10   | 12(10)         | 11(11)         | DS     | D5    | DS          | D5        | D5   | DS    | D5   | D5    |

| 2 2    | 20          | D2    | D2   | D2   | D2    | D2    | D2   | 13(11)         | (14)16         | D4     | D4    | D4          | D4        | D4   | D4    | D4   | D4    |

| 720    | SSA         | VSS   | VSS  | VSS  | VSS   | VSS   | VSS  | 14(12)         | (13)15         | D3     | D3    | D3          | D3        | D3   | D3    | D3   | D3    |

| 20     |             |       |      |      |       |       |      |                | ٦              |        |       |             |           |      |       |      |       |

Parenthesis Indicates Pin Number of 24 Pin Packages. 24 Pin Devices are Lower Justified in Pins 3 Thru 26 of 28 Pin Socket

MOSTEK'S BYTEWYDE STATIC MEMORY FAMILY Table 2

| Microprocessor              | MK2716    | MK37000   | MK34000   | MK4118A<br>4802 | MK2764    | Delay (2) |

|-----------------------------|-----------|-----------|-----------|-----------------|-----------|-----------|

| 8085A 3Mhz Clock            | -7        | -5        | -3        | 4-              | TCE = 435 | 140       |

| 8085A-2<br>5 Mhz Clock      | TCE = 270 | 4-        | F-        | 4-              | TCE = 270 | 80        |

| 8088 5Mhz Clock             | 9-        | -5        | e-        | 4-              | TCE = 355 | 95        |

| 8086 5Mhz Clock             | 9-        | -5        | ۴-        | 4-              | TCE = 355 | 95        |

| MC6800<br>1.0Mhz Clock      | 8-        | -5        | e-        | 4-              | <b>φ</b>  | 80        |

| MC6802<br>1.0Mhz            | 8-        | -5        | £-        | 4               | 8         | 80        |

| MC6809 1Mhz<br>Clock        | 8-        | -5        | -3        | 4               | 8-        | 92        |

| MC68A09<br>1.5Mhz Clock     | -5        | -5        | -3        | 4               | TCE = 345 | 92        |

| MC68B09<br>2.0Mhz Clock     | TCE = 245 | 4-        | TCE = 245 | 4-              | TCE = 245 | 75        |

| 6500 Series<br>1Mhz Clock   | 9-        | -5        | -3        | 4               | TCE = 355 | 75        |

| MK3880 Z80<br>2.5Mhz Clock  | -7        | -5        | -3        | 4-              | TCE = 440 | 165       |

| MK3880-4 Z80A<br>4Mhz Clock | TCE = 225 | TCE = 225 | TCE = 225 | 4-              | TCE = 225 | 115       |

| Z8002 4Mhz Clock            | -5        | 4         | TCE = 300 | 4-              | TCE = 300 | 100       |

NOTES 1. All "P clock speeds given are maximums allowed for each part or are in memory component selection is achieved. stated fastest device in a series. By slowing clock speeds more flexibility 2. Delay = time between µP valid address and chip enable time

EPROM and 1K x 8 to 8K x 8 of RAM, are few. The jumper connections and pin function comparisons are shown for various memory types and sizes in Table 1. The memory configuration can be expanded to 8 sockets by the addition of an extra 256 x 4 PROM address decoder. This combined with the 28 pin socket concept allows the memory to be upgraded to the  $64 \text{K} \times 8$  level as higher density memories become available.

The control functions are also very simple as shown. WR goes directly to WE, RD goes to OE and MREQ is connected to the enable on the 74S387 PROM.

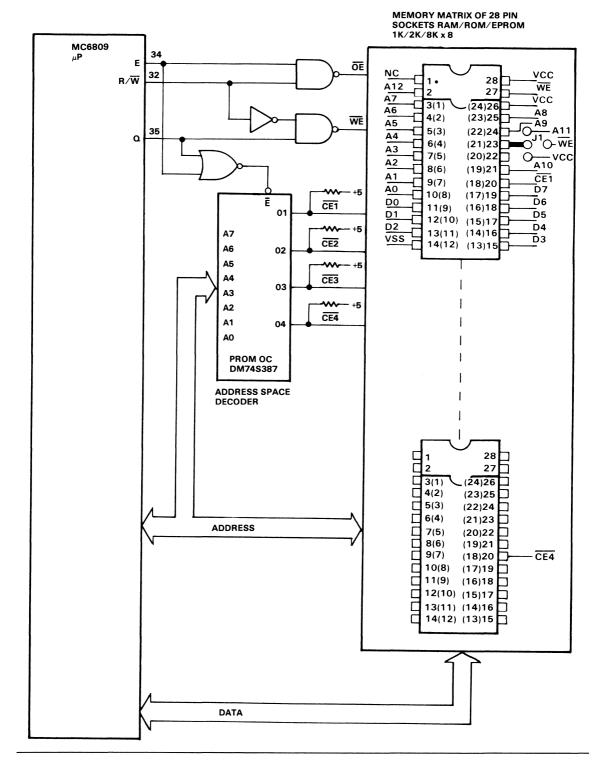

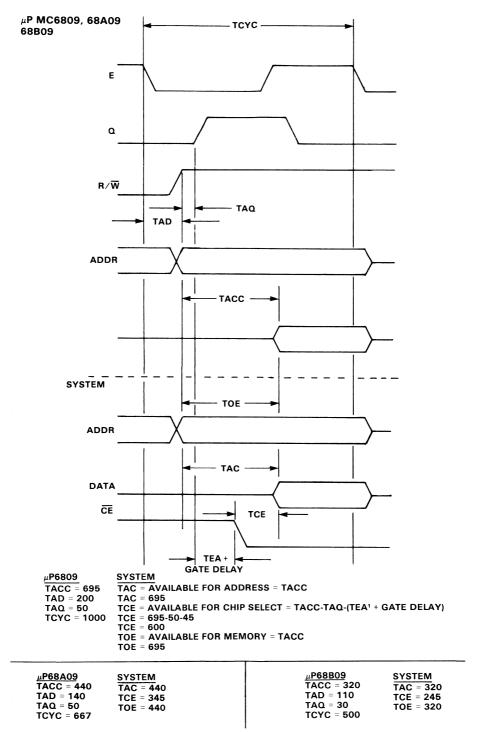

Figure 11 shows a typical connection possibility for BYTEWYDE Memory to a Motorola 6809 microprocessor. The control signals in this case require some extra logic before being connected to the memory. There are basically two reasons for this extra logic requirement. One is due to the fact that on the 6809, the  $R/\overline{W}$  controls are on the same pin. Some logic is needed to generate  $\overline{OE}$  and  $\overline{WE}$  signals.

The second reason is a combination of items. Mostek's BYTEWYDE RAMs require that data inputs be held valid after the trailing edge of  $\overline{WE}$ . In the 6809 data goes away at the same time as  $R/\overline{W}$ . The extra logic shown in Figure 11 uses the clock E and quadrature clock Q to take  $\overline{WE}$  high prior to the 6809 taking  $R/\overline{W}$  high. This insures that  $\overline{WE}$  goes high approximately one quarter cycle prior to data input going away.

In order to use the Edge Activated<sup>TM</sup> 64K ROM, E and Q are also used to enable the PROM decoder. This

provides both an active period of  $\frac{3}{4}$  of the  $\mu$ processor cycle and  $\frac{1}{4}$  of a period for  $\overline{\text{CE}}$  precharge as required by "Edge Activated" devices. All other connections to the 6809 are the same as in the MK3880.

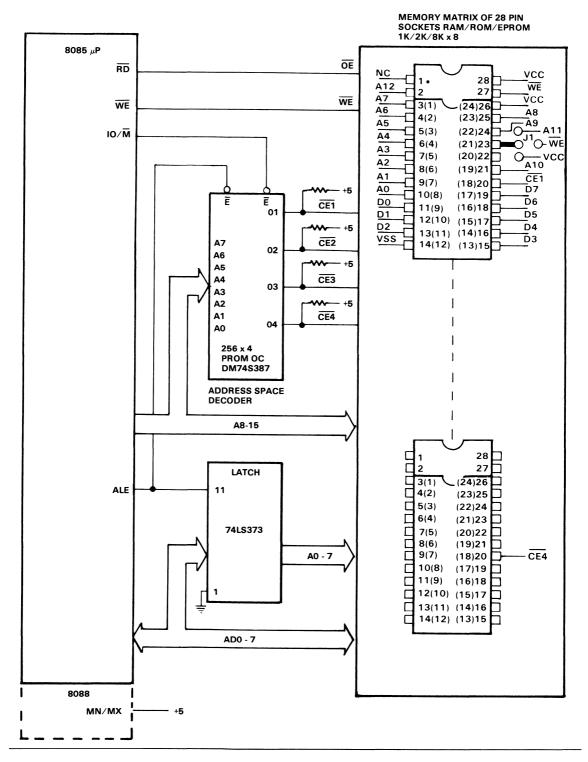

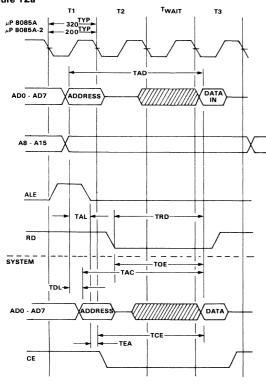

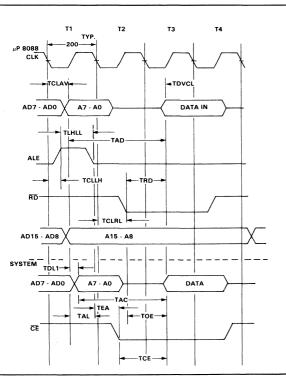

The Intel 8085/8088 (Figure 12) provides another unique situation, however again the BYTEWYDE fits quite easily. Read and write controls connect directly as in the 3880  $\mu P$ . Two microprocessor signals that require looking at are IO/ $\overline{M}$  and ALE. The IO/ $\overline{M}$  signal is used to determine whether data will be to or from an I/O device or memory. ALE is the address latch enable signal used to clock addresses into the latch so that the pins can be used for data since the 8085/8088 has common data and address lines. Therefore, IO/ $\overline{M}$  and ALE are connected to the Enable and Enable respectively of the PROM decoder.

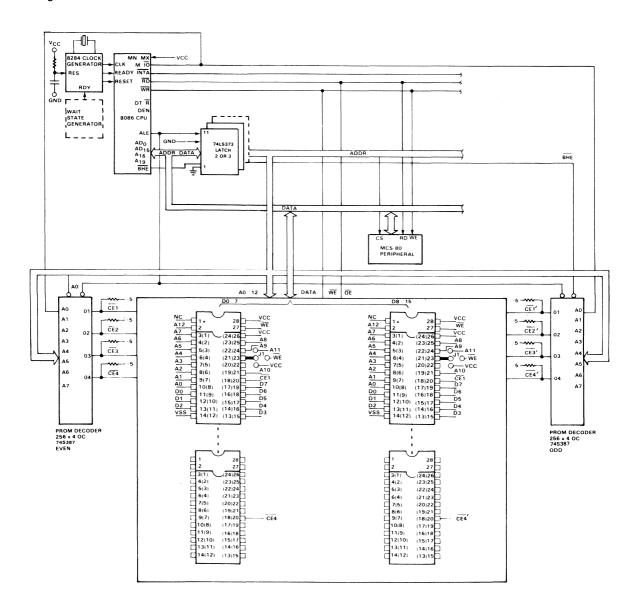

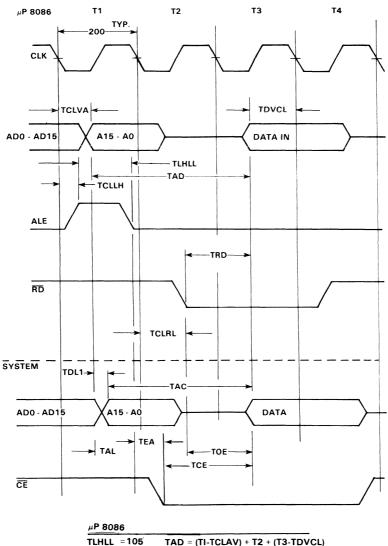

One of the new generation 16 bit microprocessors, the Intel 8086, is shown configured to the BYTEWYDE memory. The connections are the same as in the 8085 except in this case two BYTEWYDE Memories are required to handle 16 bits of data. Two PROM decoders are required to generate the  $\overline{\text{CE}}$  ( $\overline{\text{CS}}$ ) signals in order to meet the byte addressability requirements. The 8086 can pick either 8 or 16 bits at a time. Otherwise one decode would suffice.

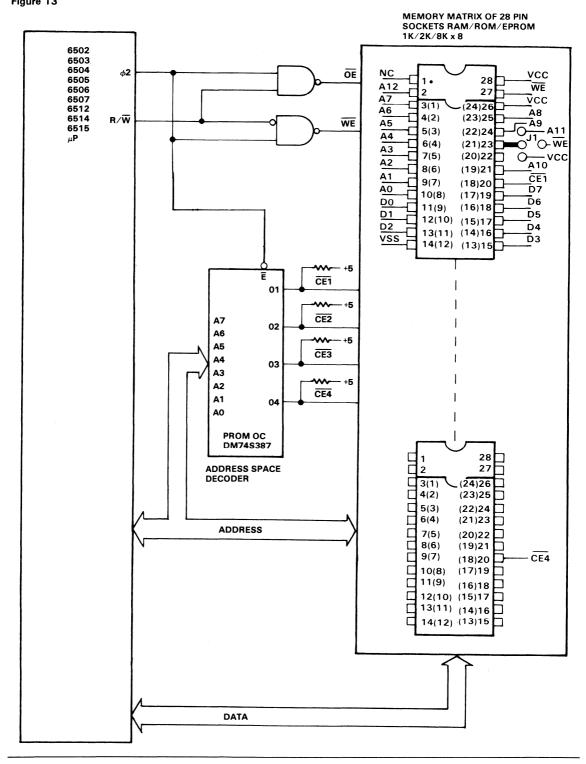

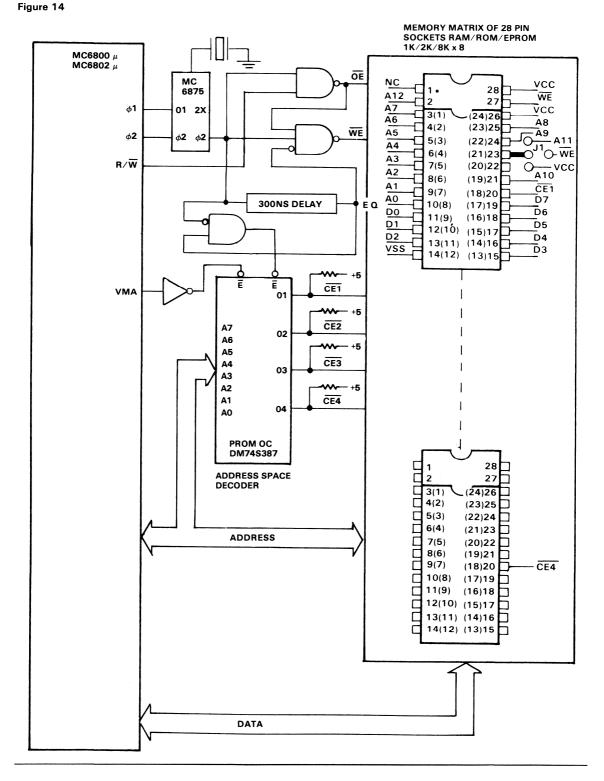

Also included in Figure 13 thru 16 are examples to interface with such popular microprocessors as the 6500, 6800, 8086, Z80 and Z-8000. Table 2 identifies the specific dash number required for each memory type to microprocessor performance characteristics.

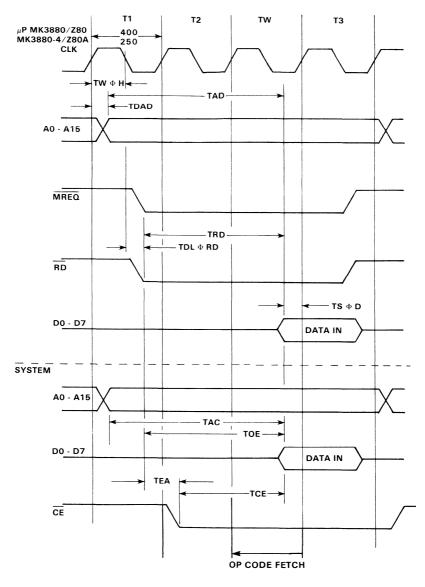

# INTERFACE TO 3880/Z80

Figure 10a

# μP MK3880 TC = T1 = 400 TAD = (T1-TDAD) + (T2-TSΦD) TDAD = 145 TAD = 255 + 350 = 605 TSΦD = 50 TRD = T1 - (TWΦH + TDLΦRD) + (T2-TSΦD) $TW\Phi H = 180$ TRD = 120 + 350 = 470 $TDL\Phi RD = 100$

# SYSTEM

TAC = AVAILABLE FOR ADDRESS ACCESS = TAD **TAC = 605** TCE = AVAILABLE FOR CHIP SELECT = TRD-TEA1

TCE = 440 TOE = AVAILABLE FOR MEMORY = TRD

TOE = 470

NOTE 1 TEA = ENABLE ACCESS TIME OF DM74S387

# μP MK3880-4

TC = 250 **TAD = 340 TDAD = 110** TRD = 255  $TS\Phi D = 50$  $TW\Phi H = 110$  $TDL\Phi RD = 85$

# **SYSTEM**

TAC = 340 TCE = 225 TOE = 255

# **INTERFACE TO 6809**

Figure 11a

NOTE 1 TEA = ENABLE ACCESS TIME of DM74S387

Figure 12

## **INTERFACE TO 8085**

# Figure 12a

SYSTEM TAC = AVAILABLE FOR ADDRESS ACCESS = TAD-TDL TAC = TAD ( $\mu$ P)-74LS373 DELAY TAC = 575-15 = 560 μP8085A TAD = 575 TRD 300

TAL - 11d TCE - AVAILABLE FOR CHIP SELECT

TCE - TAD (µP)-TAL - TEA (ENABLE ACCESS OF DM745387)

TCE = 575-140 = 435

TOE - AVAILABLE FOR MEMORY = TRD

<u>μP8085A-2</u> TAD = 350 TRD = 150

$\underline{\text{SYSTEM}}$  TAC - AVAILABLE FOR ADDRESS - TAD-TDL TAC - TAD  $(\mu P)\text{-}74\text{LS}373$  DELAY TAC - 350-15 - 335

TAL = 50

TCE = AVAILABLE FOR CHIP SELECT TCE = TAD (µP)-TAL-TEA (ENABLE ACCESS OF DM74\$387) TCE = 350-80 = 270

TOE = AVAILABLE FOR MEMORY = TRD

OE - 150

# μP 8088

TAD = (TI-TCLAV) + T2+ (T3-TDVCL) TCLAV = 110 TDVCL = 30 TAD = (200-110) + 200 + (200-30) TAD = 460 TAL = TCLLH + TLHLL - TCLAV = 75 TCLLH - 80 TIHLL = 105 TRD = (T2-TCLRL) + (T3-TDVCL)

TRD = (200-165) + (200-30)

TRD = 205 TCLRL = 10

SYSTEM

TAC = AVAILABLE FOR ADDRESS ACCESS TAD-TDL1

TAC = TAD µP -74LS373 DELAY

TAC = 460-18 = 442

TCE = AVAILABLE FOR CHIP SELECT = TAD-TAL-TEA1 TCE = 460-75-30 = 355 TOE = AVAILABLE FOR MEMORY = TRD

TOE = 205

NOTE 1 TEA - ENABLE ACCESS TIME OF DM748387

# **INTEFACE TO 6500**

Figure 13a

NOTE 1 TEA = ENABLE ACCESS TIME OF DM74S387

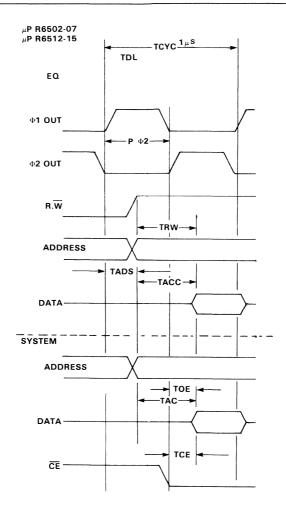

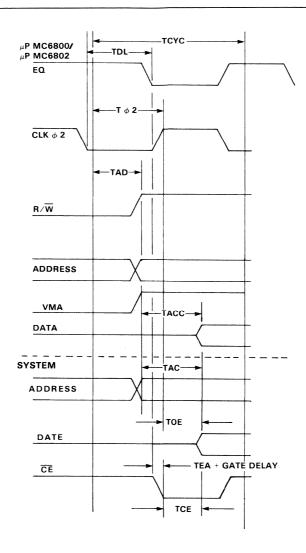

### **INTERFACE TO 6800**

Figure 14a

```

μP MC6800

μP MC6802

```

$TCYC = I \mu S$  TAD = 270

**TACC = 530**

$T\phi 2 = 500$

TDL = DELAY LINE = 300ns USING DELAY LINE OR ONE SHOT

### SYSTEM

TAC =AVAILABLE FOR ADDRESS ACCESS = TACC

**TAC = 530**

TCE = AVAILABLE FOR CHIP SELECT = TACC - (TDL - TAD) - (TEA + GATE DELAY)

TCE = 530 - 30 - (30 + 20) = 450

TOE = AVAILABLE FOR MEMORY = TACC -  $(T\phi2 - TAD)$  - GATE DELAY

TOE = 255

NOTE 1 TEA = ENABLE ACCESS TIME OF DM74S387

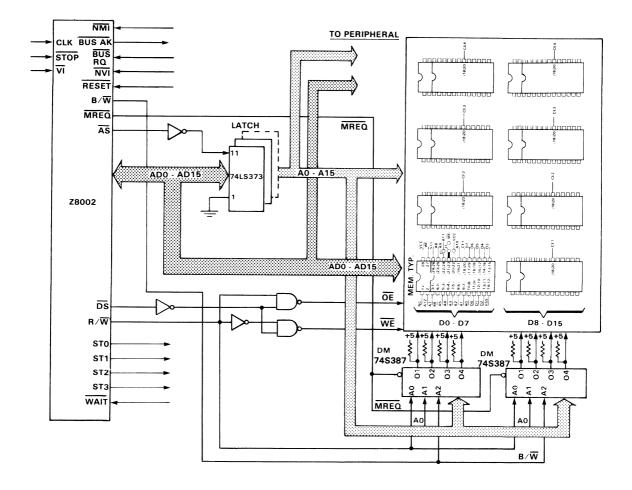

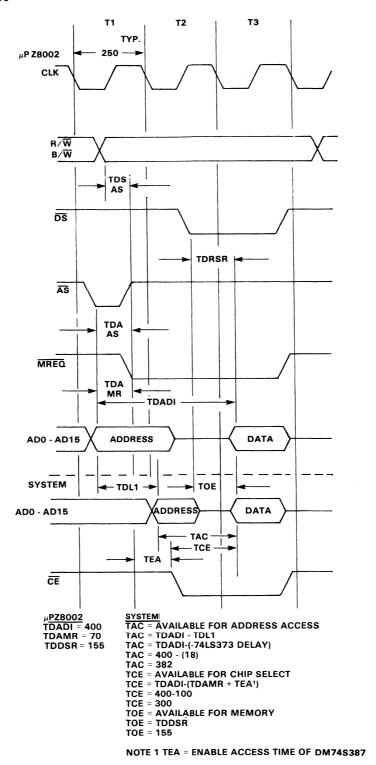

# INTERFACE TO Z8000 Figure 15

### **INTERFACE TO 8086**

### Figure 16

| TAD = (TI-TCLAV) + T2 + (T3-TDVCL) |

|------------------------------------|

| TAD = (200-110) + 200 + (200-30)   |

| TAD = 460                          |

| TAL = (TCLLH + TLHLL) -TCLAV = 75  |

| TRD = (T2-TCLRL) + (T3-TDVCL)      |

| TRD = (200 -165) + (200-30)        |

| TRD = 205                          |

|                                    |

### SYSTEM

TAC = AVAILABLE FOR ADDRESS ACCESS = TAD-TDL1 TAC = TAD( $\mu$ P)-(74LS373) TAC = 460-18 = 442 TCE = AVAILABLE FOR CHIP SELECT = TAD-TAL-TEA¹ TCE = 355 TOE = AVAILABLE FOR MEMORY = TRD TOE = 205

NOTE 1 TEA = ENABLE ACCESS TIME OF DM74S387

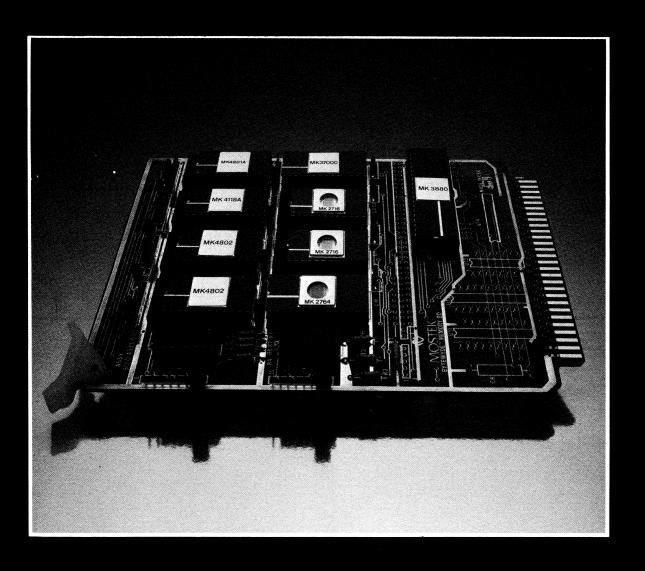

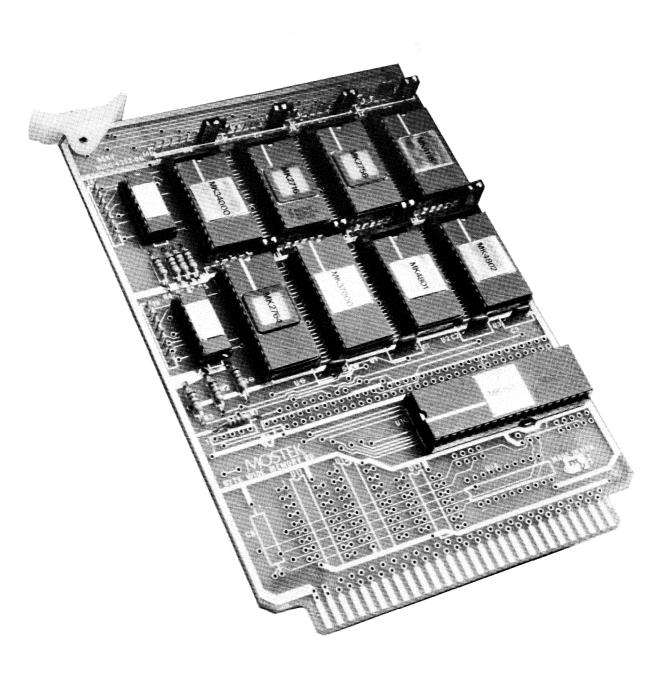

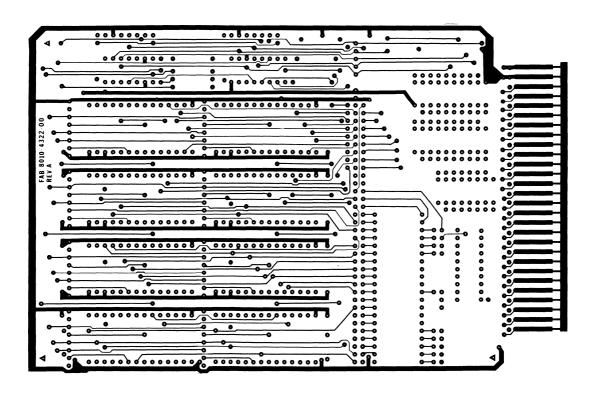

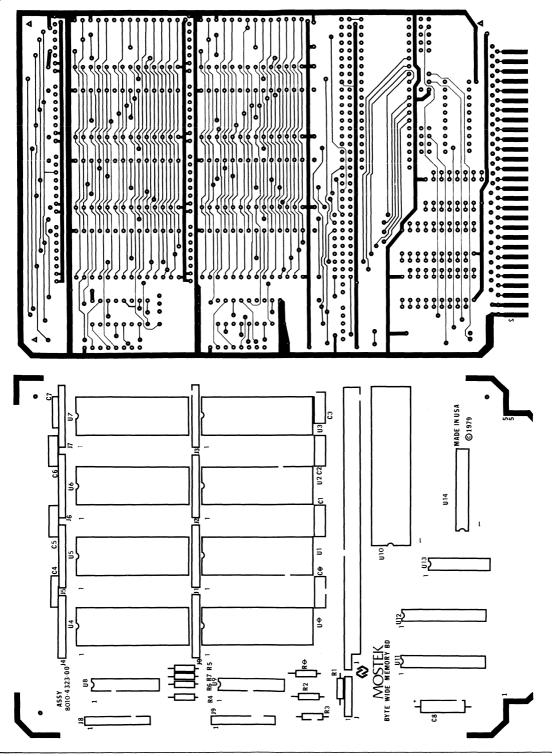

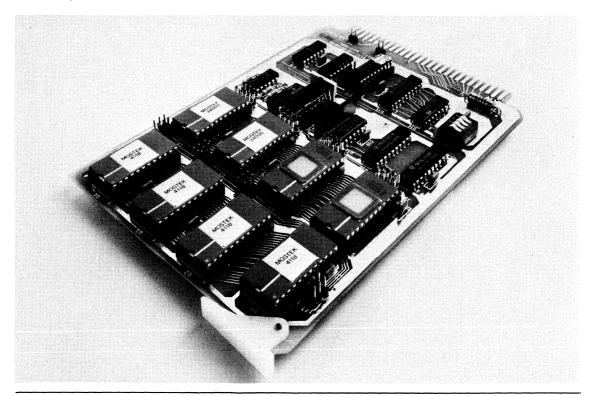

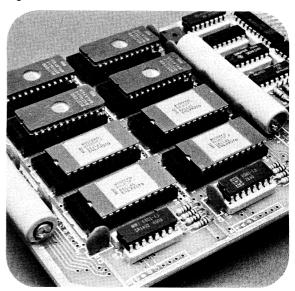

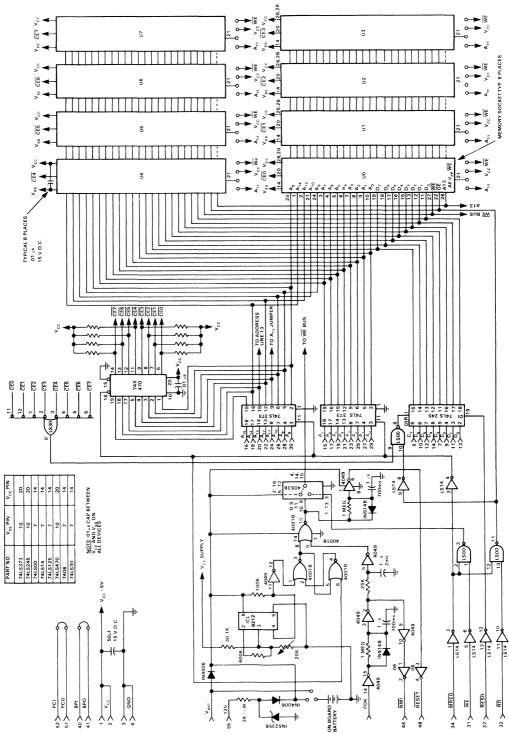

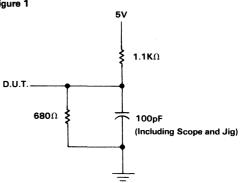

### BYTEWYDE PRINTED CIRCUIT BOARD EXAMPLE

A printed circuit board layout using Mostek's BYTEWYDE Static Memory was designed to illustrate the density and flexibility of the BYTEWYDE approach. This layout is universal i.e., ROM/EPROM/RAM, 8 bit or 16 bit. A particular system may not require an allencompassing design so simplifications are possible while still maintaining design and PC board flexibility. This design supports the following features:

- 1. 24/28 pin socket sites for present and future devices

- Individual socket jumpers to support RAM/ ROM/EPROM interchange

- Programmable address space decoder to support 1K/2K/4K/8K Byte Address space for each socket

- 4. Modular expansion in four socket increments

- 5. 8 bit or 16 bit data words

- 6. Two sided printed circuit board layout rules

Since microprocessors are well suited to this design philosophy provisions were incorporated on the printed circuit boards for a 40 pin microprocessor socket. Additional 16 and 20 pin socket sites are available to provide the latches and gates sometimes necessary to

support the processor memory interface. Figure 19 is a schematic diagram of memory interfaced to the MK3880 microprocessor.

The BYTEWYDE Memory Board is a 2 x 4 array using 28 pin sockets (U0 - U7). By lower justifying 24 pin BYTEWYDE memories, today's product can be used. By having 28 pin sockets new generations of BYTEWYDE memories can replace the 24 pin devices without redesigning the memory board.

The BYTEWYDE board has ten (8 ea.) pin jumper locations. These occupy very little space while offering a great deal of flexibility. Jumper strips (JO - J7) are located at the top of each memory socket. These stripes are for the different functions required of pins 21 and 23 in the memory array. Referring to the Mostek BYTEWYDE Static Memory Family Chart, pin 21 is for partials and 23 for ROM/RAM compatibility. Providing a jumper at each memory location allows any Mostek memory on this chart to be used in any of the 8 memory locations.

For decoding the memory array (2) 256 x 4 bipolar PROMs (U8 & U9) are used. Having two of these PROMs increases the flexibility of this board by allowing a 16 bit

PRINTED BOARD LAYOUT (SOLDER SIDE)

Figure 17

Figure 18

# 8K/16K/64/RAM/EPROM/ROM COMPATIBLE SOCKETS WITH MK3880 Figure 19

# BYTEWYDE MEMORY BOARD PARTS LIST Table 3

| Units | Designator | Description                                      |

|-------|------------|--------------------------------------------------|

| 1 ea. | P.C. Board | BYTEWYDE Memory Board                            |

| 8 ea. | U0 - U7    | 28 pin memory sockets                            |

| 8 ea. | CO - C7    | .1 μf, 25V decoupling capacitors                 |

| 8 ea. | J0 - J7    | 8 pin jumper connectors for each memory location |

| 8 ea. | RO - R7    | 1K Ω 5% resistors ¼ W                            |

| 2 ea. | U8 & U9    | 16 pin sockets for PROMs                         |

| 2 ea. | J8 & J9    | 8 pin jumper connections for PROMs               |

| 1 ea. | U10        | 40 pin socket for microprocessor                 |

| 4 ea. | U11 - U14  | μP interfacing sockets                           |

| 1 ea. | C8         | 15μf, 15V electrolytic capacitor                 |

microprocessor to interface to the memory array. Added versatility is made via the 2 jumper strips (J8 & J9). These strips allow use of the AO address and  $\overline{\text{BHE}}$  signal for the odd and even bytes which are needed by a 16 bit  $\mu P$ . The data lines coming from the array are split into two groups, the upper array and lower; therefore, the DO - D7 and D8 - D15 distinction.

The 40 pin socket location is for the microprocessor. The Mostek 3880  $\mu$ P can most easily be wired, but any  $\mu$ P can be used because of the universality which has been built into this board.

Four locations have been designated to generate gating, timing, and latching requirements for certain  $\mu$ P's. These locations are intended to be wire wrap sockets.

For more details on how to design a memory array for flexibility and expandibility without redesigning your memory each time, contact your Mostek Field Applications Engineer.

### **MICROPROCESSOR MEMORY ALTERNATIVES**

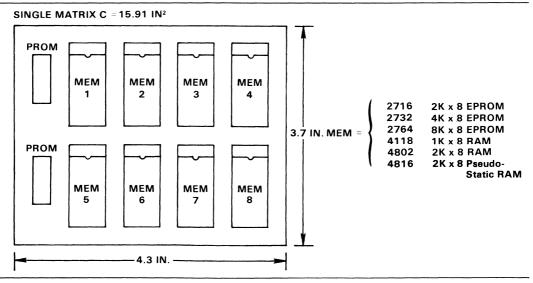

Implementing microprocessor memory designs with a coherent packaging strategy enhances density. Mostek's BYTEWYDE Static Memory Family of RAM, ROM and EPROM make possible high density memory, yet allow for flexibility and future expansion. The commonly used approaches to build microprocessor memory are restrictive in that ROM and RAM do not share the same package.

Most microprocessor based systems require a portion of their memory to be nonvolatile, namely ROM. The exact mixture of ROM and RAM is rarely known at design time and frequently changes during the course of the product life. A substantial amount of the p.c. board space is conserved with a single matrix of 24/28 pin packages is designed, as opposed to the two matrixes, each having their own spare requirements for expansion.

Memory designs normally allow for memory expansion by providing spare sockets in the memory matrix. If RAM is chosen to be packaged and pin incompatible with ROM then two memory matrixes are required, each with their own expansion spare sockets. Given that exact requirements are rarely known at design time, this results in excessive unused p.c. board real estate because each matrix has it's own expansion requirements. An alternative is to choose a RAM which

### JUMPER LAYOUT FOR MEMORY

Figure 20

is upgradable and plug compatible with ROM. In this way, a single memory matrix can be layed out. RAM and ROM can be mixed at will, causing fewer constraints to be placed on the memory configuration.

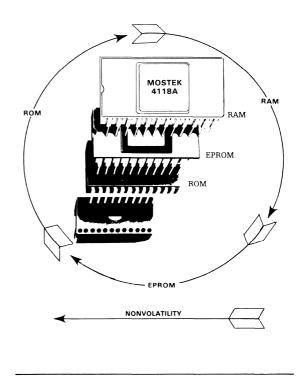

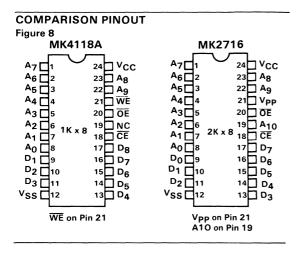

The Mostek MK4118 1K x 8 RAM is pin compatible with MK2716 2K x 8 EPROM and MK34000 2K x 8 ROM. Expansion can be accomplished by using the next generation higher density components which will be pin compatible with presently available BYTEWYDE memory.

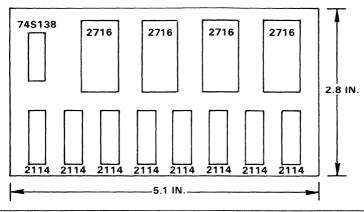

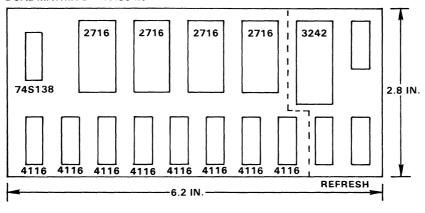

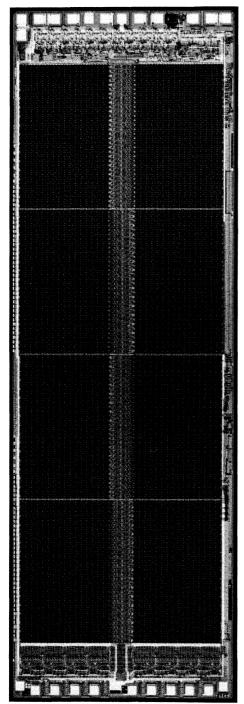

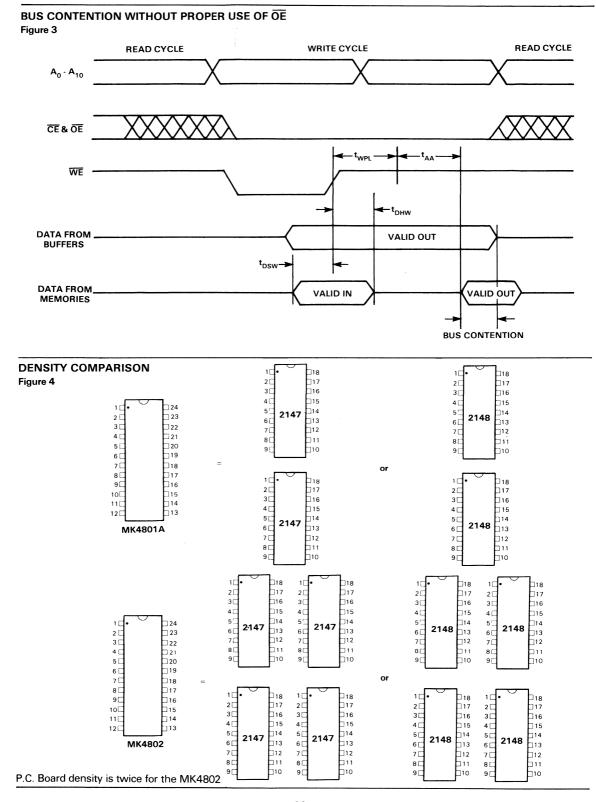

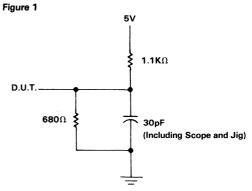

Density has and will continue to be an important criteria used to evaluate memory component selection. The two most popular microprocessor RAMs today are the 4118 1K x 8 and the 2114 1K x 4. The printed circuit board space requirement for the 1K x 8 of memory using 4118 is the same as using (2) 2114. However, the 2114 lacks ROM/EPROM compatibility and the 2114 cannot be expanded in density without package redesign. The 4118 will have a double density pin compatible upgrade 4802. The 4802 2K x 8 will be four times the density of the 2114 and requires half the board real estate.

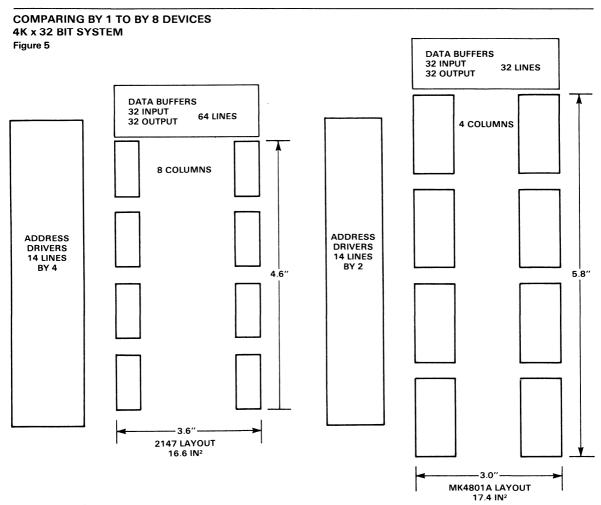

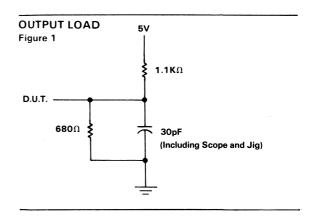

A comparative analysis of current technology alternatives for implementing 4K x 8 RAM plus 8K x 8 EPROM memory has been performed. The printed circuit board density has been determined using 2 sided p.c. board layout rules. The advantages and disadvantages of each approach are summarized in a Table 4 and Figure 21.

### **BOARD LAYOUT SPACE COMPARISONS**

Figure 21

DUAL MATRIX A = 14.28 IN<sup>2</sup>

### DUAL MATRIX B = 17.36 IN<sup>2</sup>

# COMPARATIVE ANALYSIS TABLE Table 4

|                              | Matrix A                    | Matrix B                     | Matrix C                       |  |  |  |  |

|------------------------------|-----------------------------|------------------------------|--------------------------------|--|--|--|--|

| Operation                    | Static                      | Dynamic                      | Static                         |  |  |  |  |

| RAM-ROM/PROM<br>Mixture      | Fixed at Design             | Fixed at Design              | Flexible-Any Mixture           |  |  |  |  |

| Incremental RAM<br>Expansion | 1K Bytes                    | 16K Bytes                    | 1K Bytes                       |  |  |  |  |

| EPROM Upgrade                | 2732 (4K x 8)               | 2732 (4K x 8)                | 2732 (4K × 8)<br>2764 (8K × 8) |  |  |  |  |

| RAM Upgrade                  | None                        | 4164 (64K x 1)               | 4802 (2K x 8)<br>4804 (4K x 8) |  |  |  |  |

| KBytes per IN <sup>2</sup>   | 1.19                        | 1.45                         | 1.33                           |  |  |  |  |

| Ultimate Matrix<br>Capacity  | 16K x 8 EPROM<br>4K x 8 RAM | 16K x 8 EPROM<br>64K x 8 RAM | > 64K x 8<br>Any Mixture       |  |  |  |  |

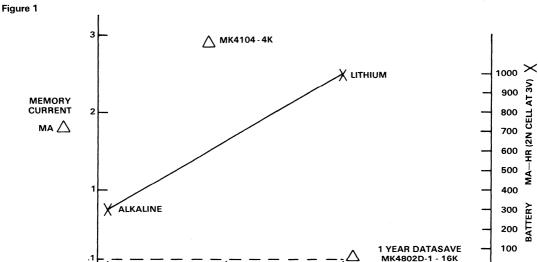

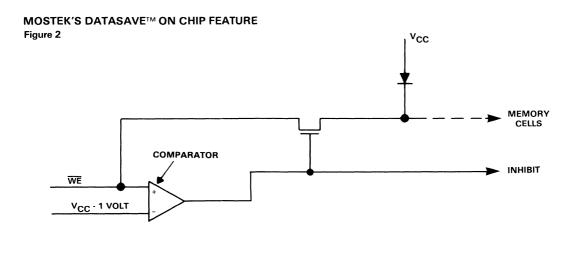

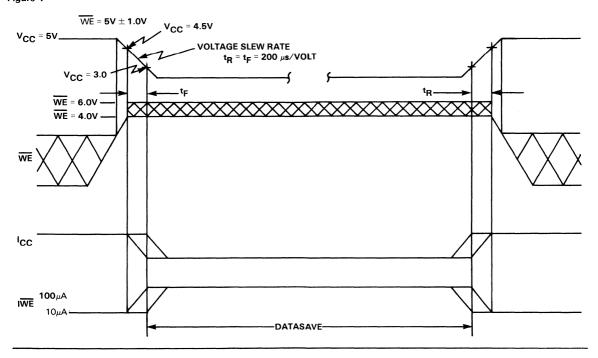

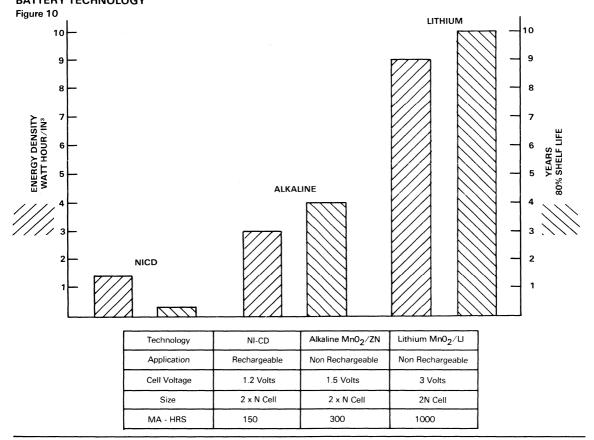

### CONCLUSION